Agilent 81250 Parallel Bit Error Ratio Tester

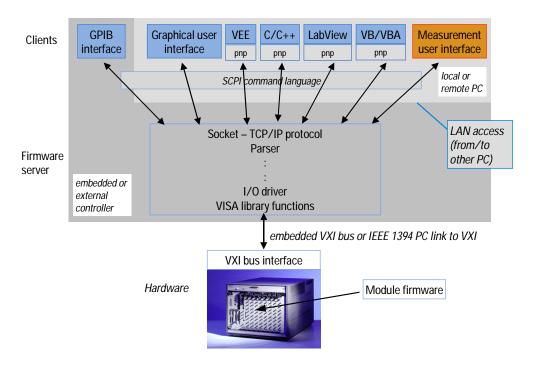

**System User Guide**

#### **Important Notice**

© Agilent Technologies, Inc. 2003

#### **Manual Part Number**

5988-4887EN

#### Revision

Revision 5.1, February 2003

Printed in Germany

Agilent Technologies Herrenberger Straße 130 D-71034 Böblingen Germany

Authors: t3 medien GmbH

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### **Safety Notices**

#### **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING/DANGER

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### **Trademarks**

Windows NT ® and MS Windows ® are U.S. registered trademarks of Microsoft Corporation.

# Contents

| About this Guid | e                                       | 11 |

|-----------------|-----------------------------------------|----|

|                 | Structure of the System User Guide      | 12 |

|                 | General Structure                       | 12 |

|                 | Contents of the Chapters                | 13 |

|                 | About the ParBERT Measurement Software  | 15 |

|                 | About Special ParBERT Applications      | 16 |

| What's New?     |                                         | 17 |

|                 | Major Changes in Rev. 5.1               | 18 |

|                 | Major Changes in Rev. 5.0               | 20 |

|                 | Major Changes in Rev. 4.5               | 23 |

|                 | Major Changes in Rev. 4.3               | 26 |

|                 | Major Changes in Rev. 4.2               | 27 |

|                 | Major Changes in Rev. 4.1               | 30 |

|                 | Major Changes in Rev. 4.0               | 33 |

| Introduction to | the System                              | 37 |

|                 | System Capabilities                     | 38 |

|                 | Verify and Characterize Digital Devices | 38 |

|                 | Key Features                            | 39 |

|                 | System Components                       | 40 |

|                 | Mainframes and Controllers              | 40 |

|                 | Modules                                 | 43 |

|                 | Frontends                               | 53 |

|                 | Trigger Pod                             | 55 |

|                 | Identification of Hardware Resources    | 56 |

|                 | Summary of Hardware-Related Terms       | 57 |

|                 | Operating Principles                    | 58 |

|                 | Virtual Systems                         | 58 |

|                 | Hardware and Setup Models               | 60 |

|                 | Software Structure                      | 62 |

|                 | Summary of Setup-Related Terms          | 65 |

| Timing Principles                                   | 66  |

|-----------------------------------------------------|-----|

| Choice of Clock Sources                             | 66  |

| Frequency Multiplier and Segment Resolution         | 68  |

| Adding 675 Mbit/s Generator Signals                 | 73  |

| Signal Delay Compensation                           | 75  |

| Trigger-Controlled Start and Stop                   | 76  |

| Summary of Timing-Related Terms                     | 77  |

| Data Generation Principles                          | 78  |

| <b>Emulate Real Pattern and Waveform Conditions</b> | 78  |

| Data Sequences                                      | 79  |

| Data Blocks                                         | 80  |

| Data Segments                                       | 81  |

| Properties of Real Segments                         | 82  |

| Loops                                               | 84  |

| Hardware Dependencies                               | 85  |

| Summary of Data-Related Terms                       | 86  |

| Principles of Analyzer Sampling Point Adjustment    | 87  |

| Manual Analyzer Sampling Delay Adjustment           | 88  |

| Automatic Delay Alignment                           | 90  |

| Automatic Bit Synchronization                       | 92  |

| Comparison of the Methods                           | 96  |

| Fast Bit Synchronization                            | 97  |

| Summary of Synchronization-Related Terms            | 100 |

| Data Capturing and Analysis Principles              | 101 |

| Functional Tests                                    | 101 |

| Error Analysis and Marginal Tests                   | 103 |

| Display of Test Results                             | 103 |

| Summary of Analysis-Related Terms                   | 104 |

| Event Handling Principles                           | 104 |

| Usage of Events                                     | 105 |

| What is an Event?                                   | 105 |

| Actions Upon an Event                               | 106 |

| Summary of Event-Related Terms                      | 106 |

| ParBERT 43/45G Systems                              | 107 |

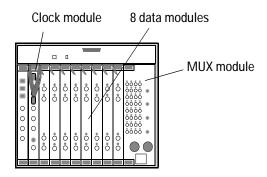

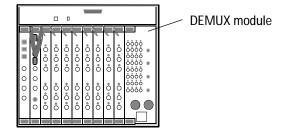

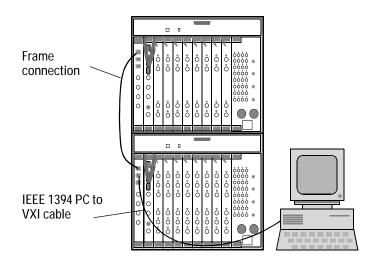

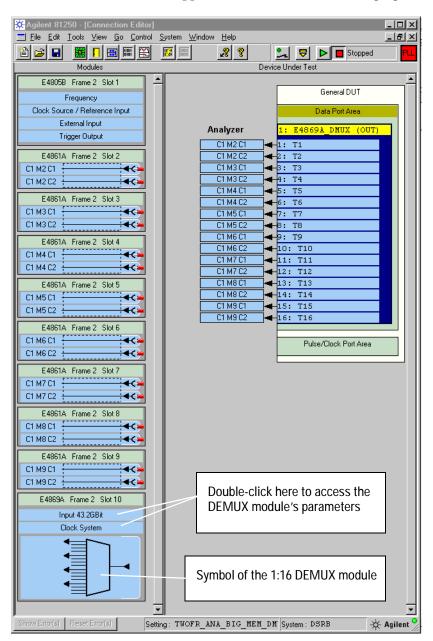

| ParBERT 43/45G Components                           | 108 |

| ParBERT 43/45G Configurations                       | 110 |

| ParBERT 43G Software Support                        | 112 |

| Automatic Rewiring of Demultiplexer Terminals | 119 |

|-----------------------------------------------|-----|

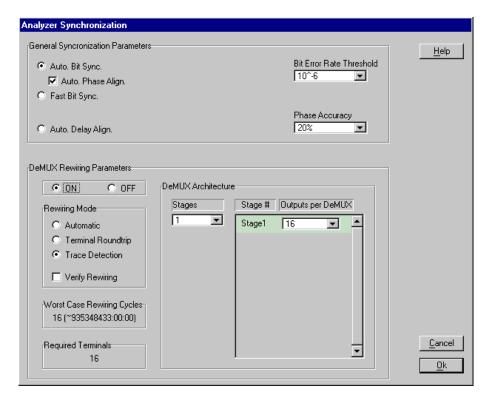

| DEMUX Rewiring Overview                       | 120 |

| DEMUX Rewiring Modes                          | 122 |

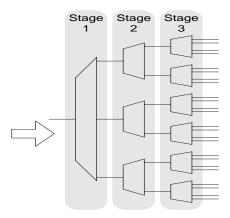

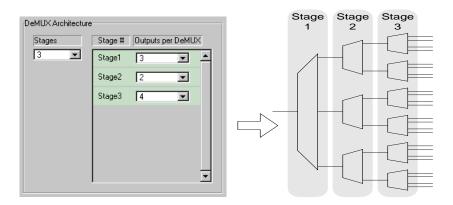

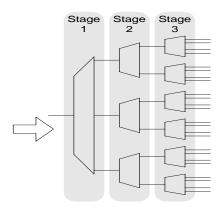

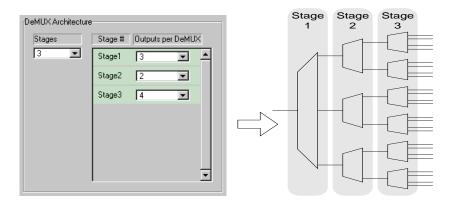

| Demultiplexer Architecture                    | 124 |

| Test Development Overview                     | 127 |

| Procedure for Setting Up the Test             | 128 |

| Procedure for Running the Test                | 130 |

| Procedure for Viewing Test Results            | 131 |

| Procedure for Saving the Test Setting         | 132 |

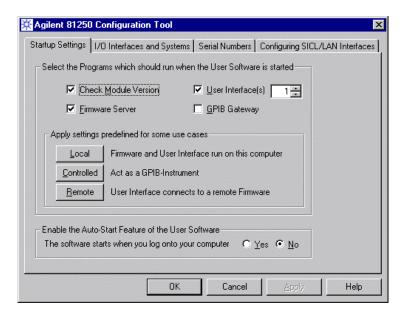

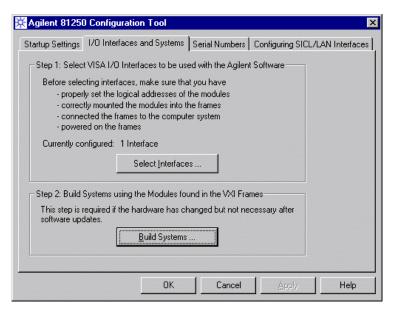

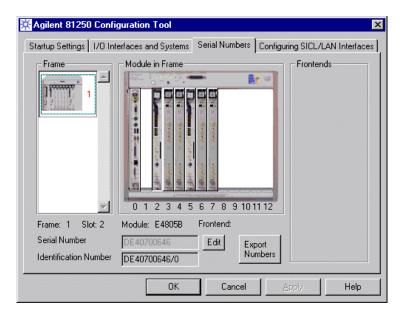

| System Start and User Interface               | 133 |

| How to Start the System                       | 134 |

| How to Start the Agilent 81250 Software       | 134 |

| How to Configure the User Interface           | 140 |

| How to Control the GPIB Gateway               | 143 |

| Overview of the Windows                       | 145 |

| Overview of Test Setup Windows                | 145 |

| Overview of Test Result Windows               | 146 |

| Operating the User Interface                  | 147 |

| How to Use the Mouse or Touchpad              | 147 |

| How to Navigate With the Keyboard             | 148 |

| How to Change Units and/or Vernier Steps      | 148 |

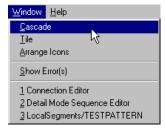

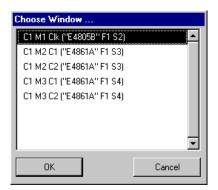

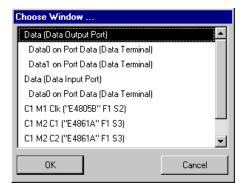

| How to Use the Window Selection Box           | 149 |

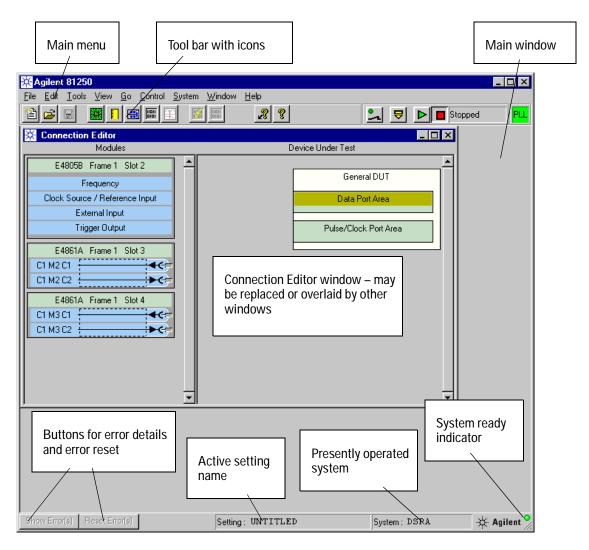

| Items of the Main Window                      | 150 |

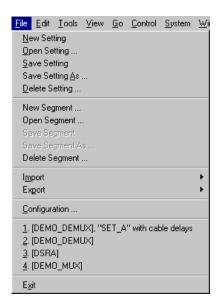

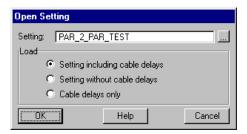

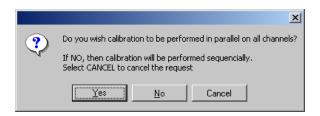

| File Menu                                     | 153 |

| Edit Menu                                     | 159 |

| Tools Menu                                    | 163 |

| View Menu                                     | 164 |

| Go Menu                                       | 166 |

| Control Menu                                  | 168 |

| System Menu                                   | 169 |

| Window Menu                                   | 171 |

| Help Menu                                     | 172 |

| Setting Global System Parameters                     | 175    |

|------------------------------------------------------|--------|

| How to Start the Parameter Editor                    |        |

| for Global Parameters                                | 176    |

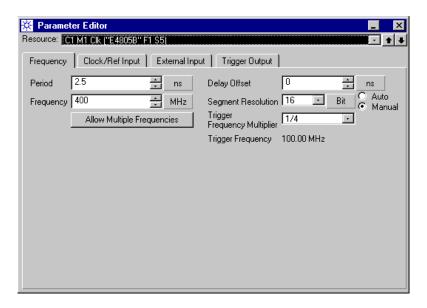

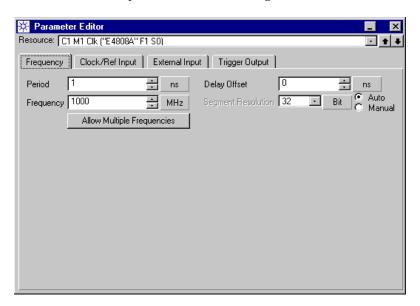

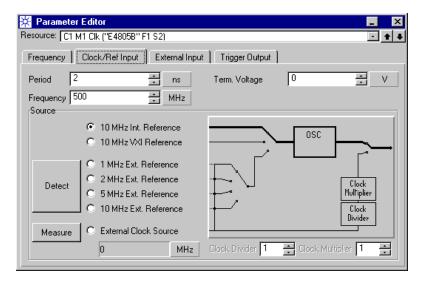

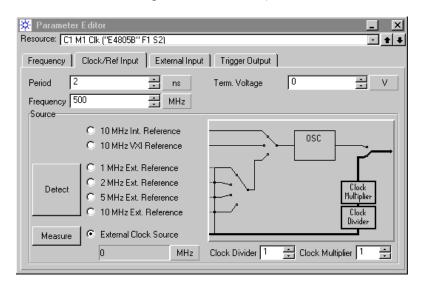

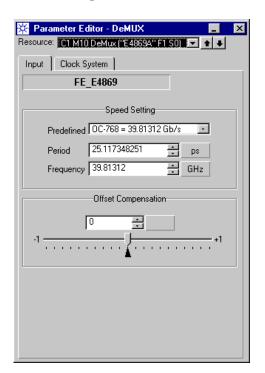

| How to Set the Clock Frequency                       | 177    |

| How to Set the General System Frequency              | 178    |

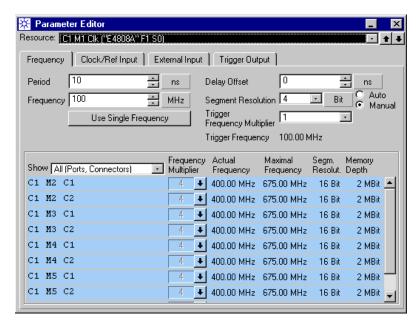

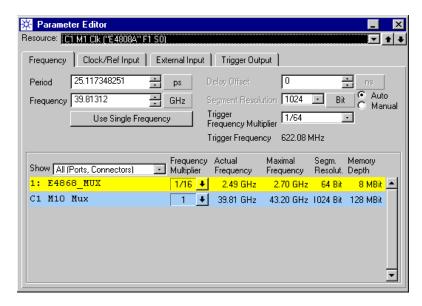

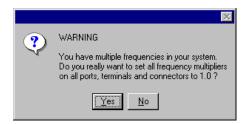

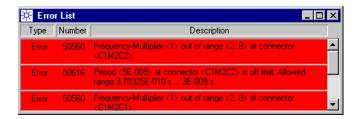

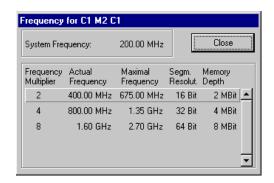

| How to Use Multiple Frequencies                      | 182    |

| How to Choose the Clock Source                       | 187    |

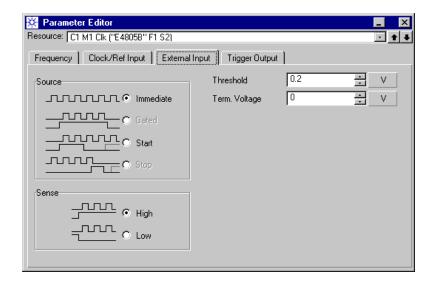

| How to Set the Characteristics of the External Input | 190    |

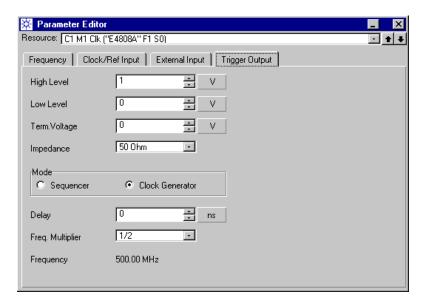

| How to Set the Characteristics of the Trigger Output | 192    |

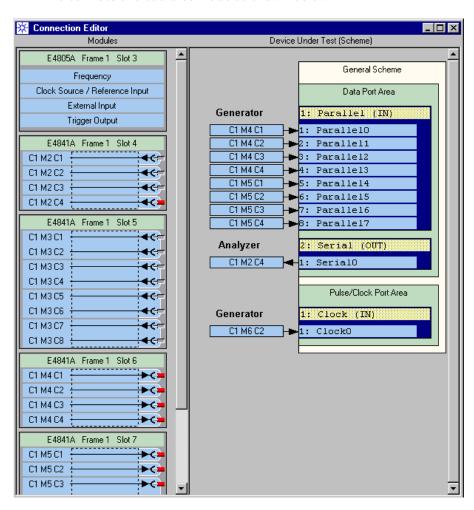

| Connecting the DUT                                   | 195    |

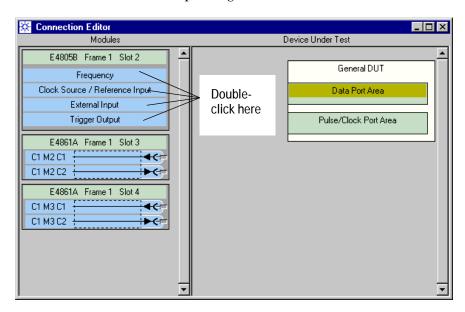

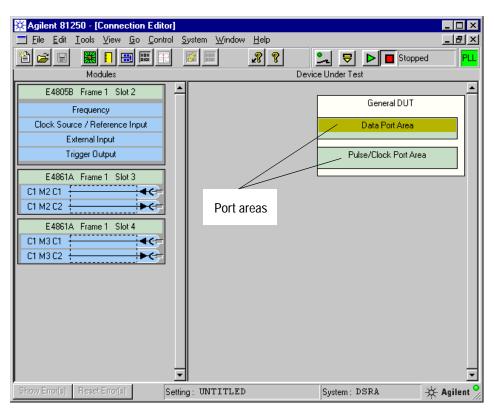

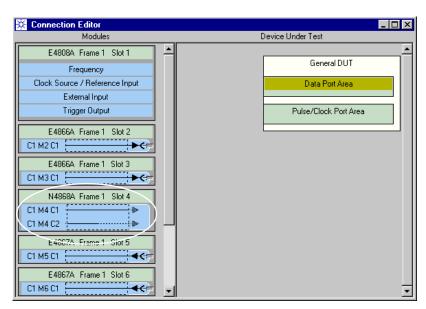

| How to Start the Connection Editor                   | 197    |

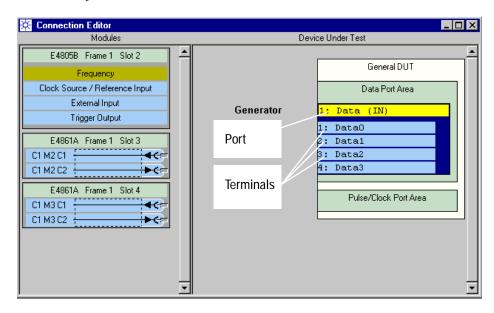

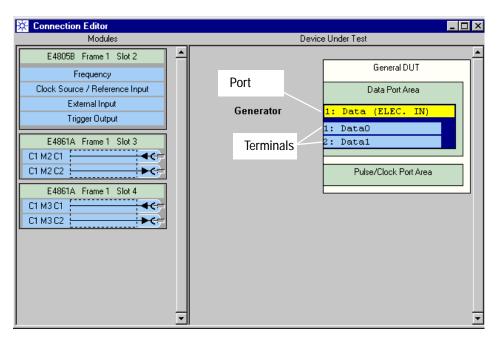

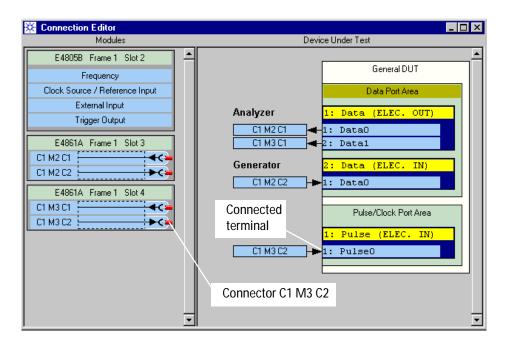

| Contents of the Connection Editor Window             | 197    |

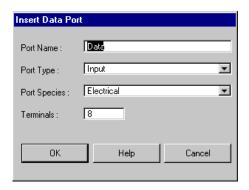

| How to Create a Port                                 | 198    |

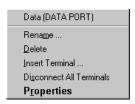

| How to Change the Characteristics of a Port          | 201    |

| How to Delete a Port                                 | 202    |

| How to Rename a Port                                 | 202    |

| How to Add a Terminal to a Port                      | 202    |

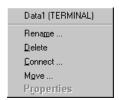

| How to Change the Characteristics of a Terminal      | 203    |

| How to Rename a Terminal                             | 203    |

| How to Delete a Terminal                             | 204    |

| How to Move a Terminal                               | 204    |

| How to Connect a Terminal                            | 204    |

| How to Disconnect a Terminal                         | 208    |

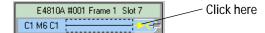

| How to Set the Mode of an Optical-Electrical Connect | or 209 |

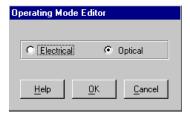

| How to Set Up a 43G MUX/DEMUX Module                 | 210    |

| How to Change the Output Parameters of a MUX Module  | 213    |

| How to Change the Clock Routing of a MUX Module      | 218    |

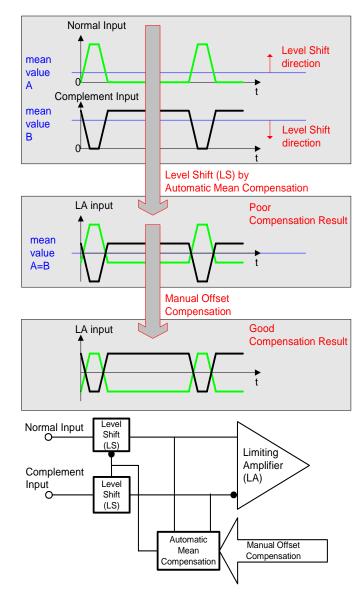

| How to Change the Input Parameters of a DEMUX Module | 219    |

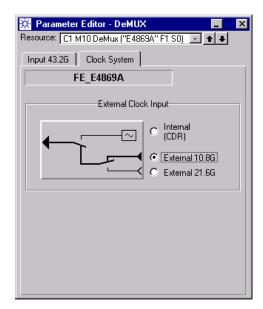

| How to Change the Clock Routing of a DEMUX Module    | 223    |

| Setting Up Ports and Channels                           | 225          |

|---------------------------------------------------------|--------------|

| How to Start the Parameter Editor for Ports/Channels    | 226          |

| How to Set Up a DUT Input Port or Generator Channel     | 228          |

| How to Set Generator Timing Parameters                  | 229          |

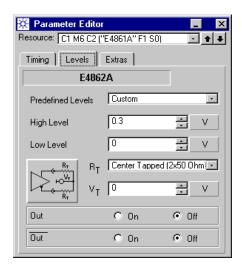

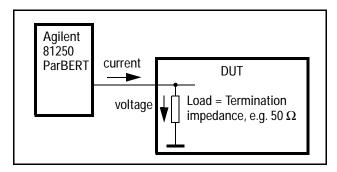

| How to Set Electrical Generator Levels and Termination  | 234          |

| How to Set Optical Generator Levels                     | 238          |

| How to Use the Variable Delay (FEs of Type E4862B Only) | 240          |

| How to Set the Global Disconnect Mode                   | 241          |

| How to Add Channels in Analog Mode                      | 242          |

| How to Set Up a DUT Output Port or Analyzer Channel     | 246          |

| How to Set Analyzer Timing Parameters                   | 247          |

| How to Set Analyzer Levels and Termination              | 247          |

| How to Set Optical Analyzer Levels                      | 250          |

| How to Combine Generator Channels                       | 253          |

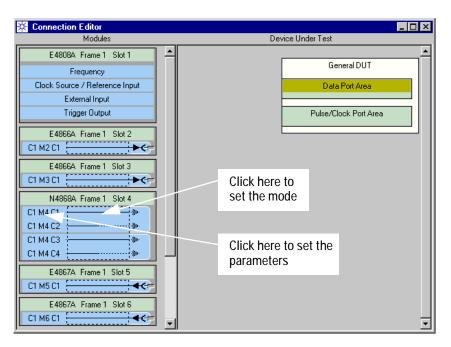

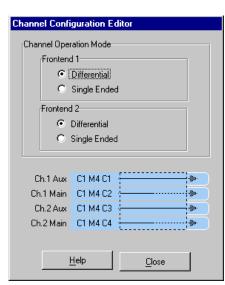

| How to Start the Channel Configuration Editor           | 254          |

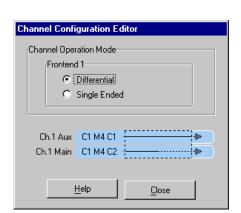

| How to Use the Channel Configuration Editor             | 255          |

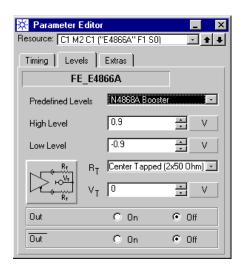

| How to Set Up N4868A Booster Channels                   | 257          |

| How to Set the Operating Mode of the Booster Module     | 259          |

| How to Set the Parameters of the Booster Module         | 260          |

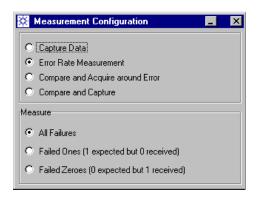

| Choosing the Kind of Measurement                        | 263          |

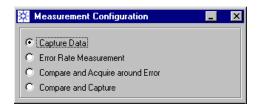

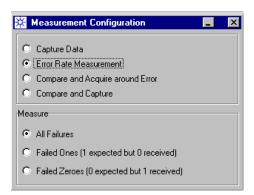

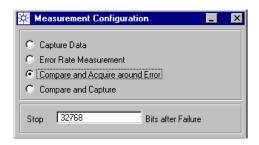

| How to Open the Measurement Configuration Window        | <b>V</b> 264 |

| How to Set the Measurement Configuration                | 264          |

| Capture Data                                            | 265          |

| Error Rate Measurement                                  | 265          |

| Compare and Acquire Around Error                        | 265          |

| Compare and Capture                                     | 266          |

| Creating the Stream of Generated and Expected Data      | 267          |

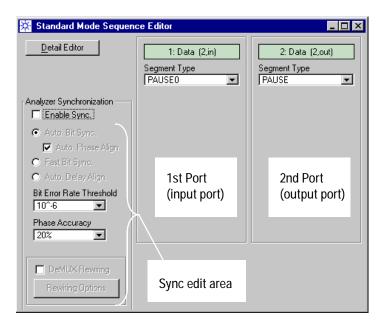

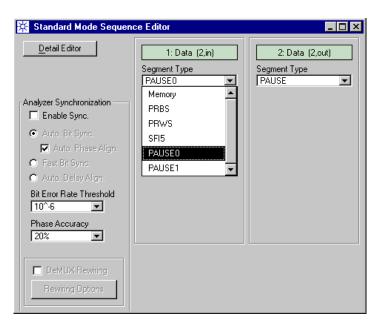

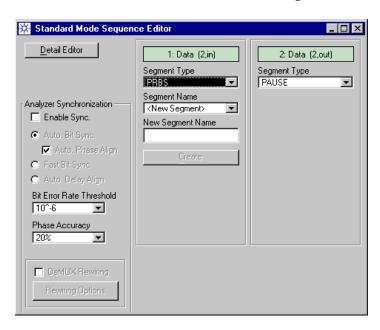

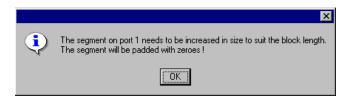

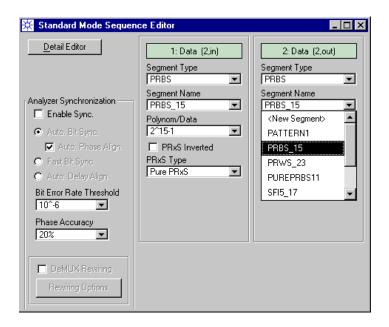

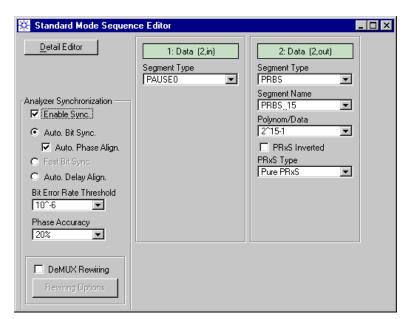

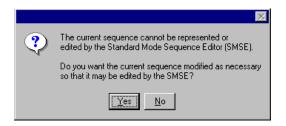

| The Standard Mode Sequence Editor                       | 268          |

| How to Use the Standard Mode Sequence Editor            | 269          |

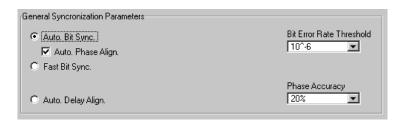

| How to Synchronize an Analyzer With Incoming Data       | 274          |

| How to Specify DEMUX Rewiring Parameters                | 280          |

| Characteristics of the Standard Mode Sequence Editor    | 285          |

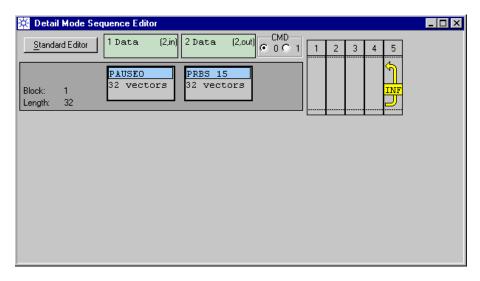

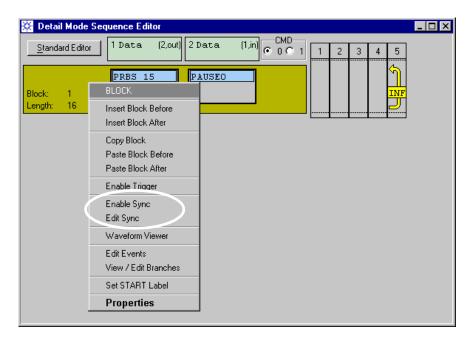

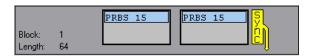

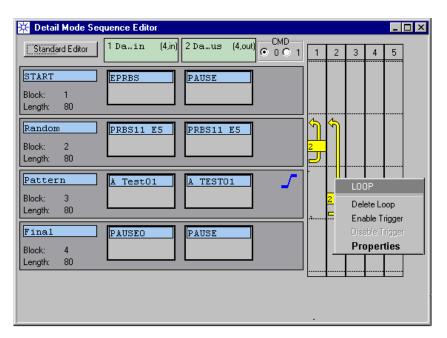

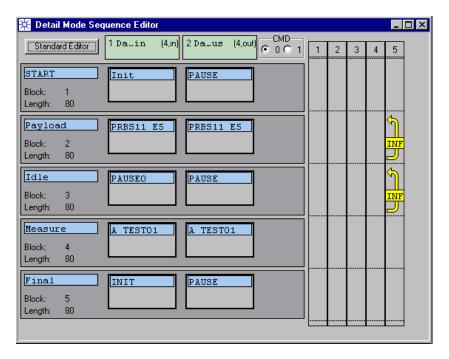

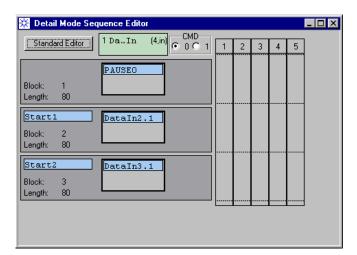

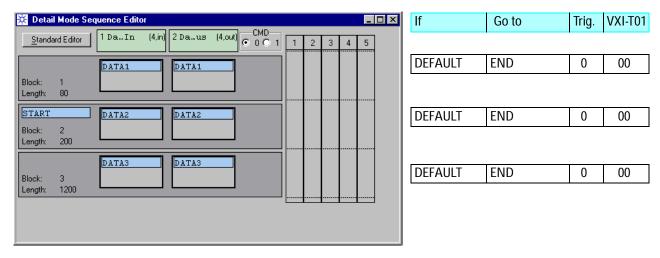

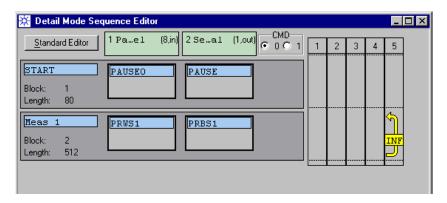

| The Detail Mode Sequence Editor                | 288      |

|------------------------------------------------|----------|

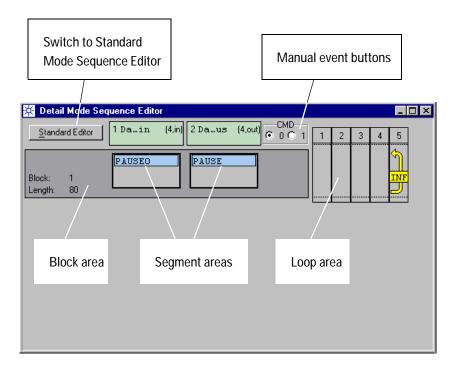

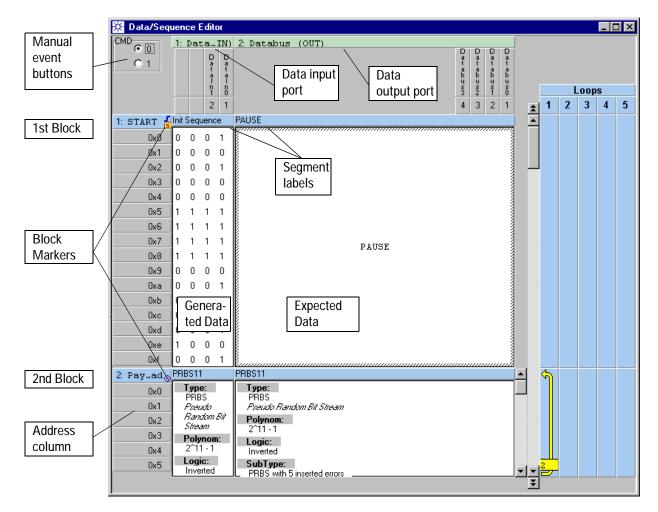

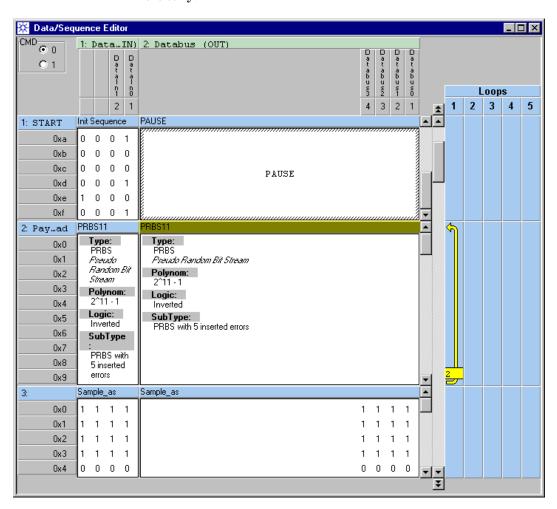

| Contents of the Detail Mode Sequence Editor Wi | ndow 289 |

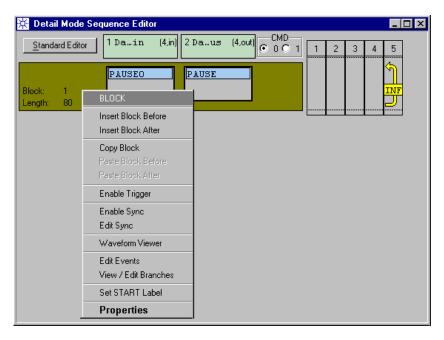

| How to Add, Move or Delete Blocks              | 290      |

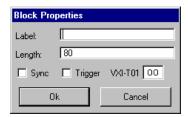

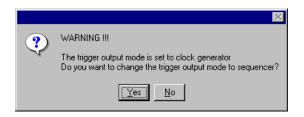

| How to Change Block Properties                 | 291      |

| How to Use a Block for Analyzer Sampling Point |          |

| Adjustment                                     | 293      |

| How to Replace the Current Segment             | 294      |

| How to Create and Change Loops                 | 298      |

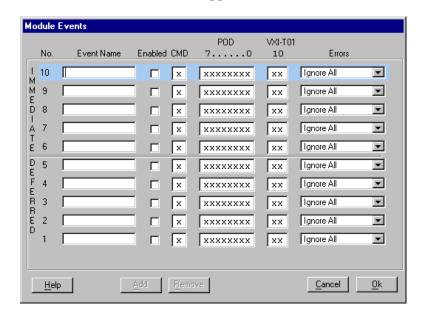

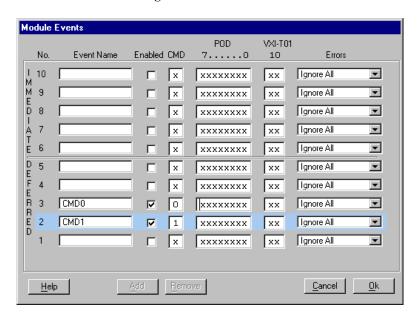

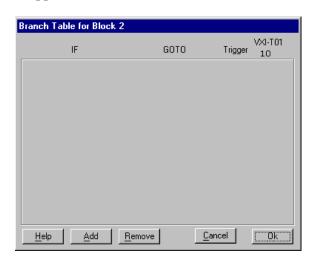

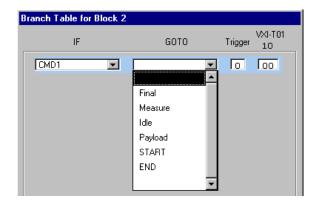

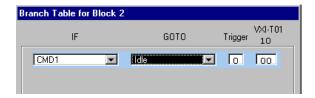

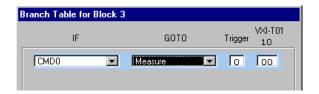

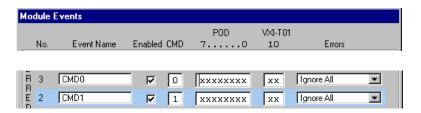

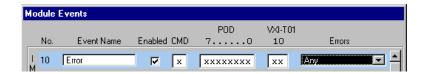

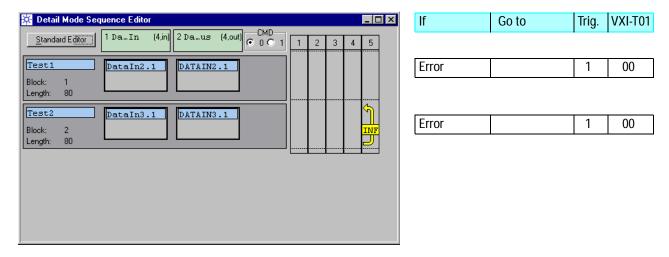

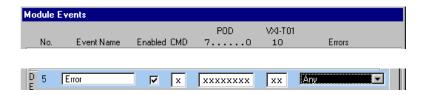

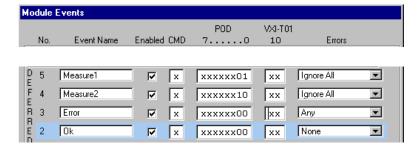

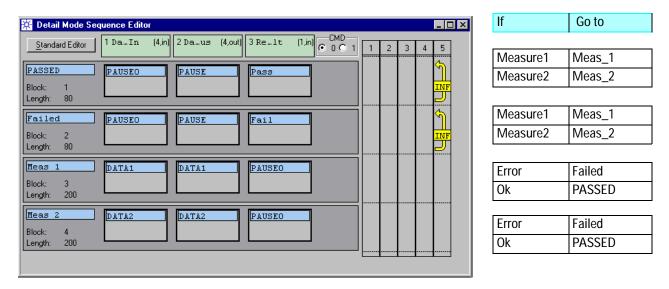

| How to Specify Events and Reactions Upon Ev    | ents 300 |

| Before You Start Using Events                  | 301      |

| How to Define Events                           | 305      |

| How to Specify the Reactions on Events         | 307      |

| Creating and Editing Segments                  | 311      |

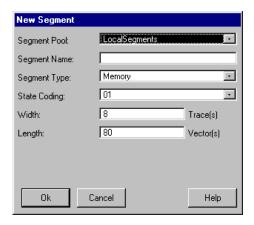

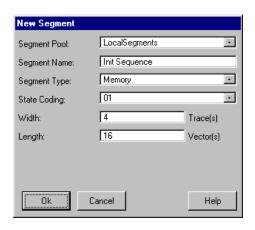

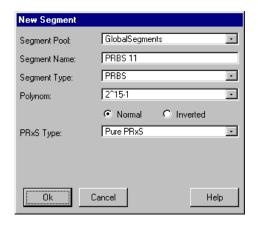

| How to Create a New Segment                    | 312      |

| How to Start Creating a New Segment            | 313      |

| How to Create a Memory Segment                 | 314      |

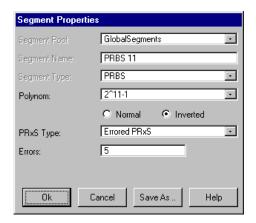

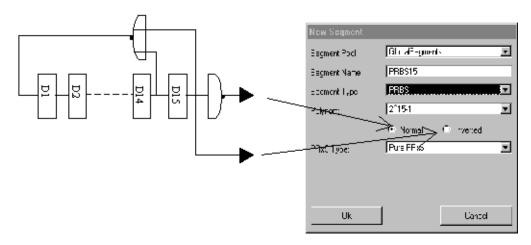

| How to Create a PRBS/PRWS Segment              | 321      |

| How to Save a New or Changed Segment           | 323      |

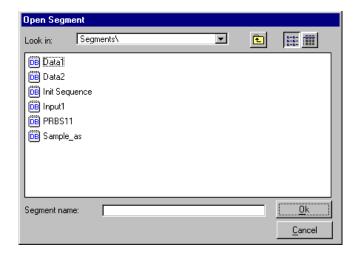

| How to Edit a Stored Segment                   | 323      |

| How to Select a Segment                        | 324      |

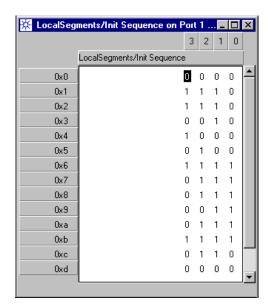

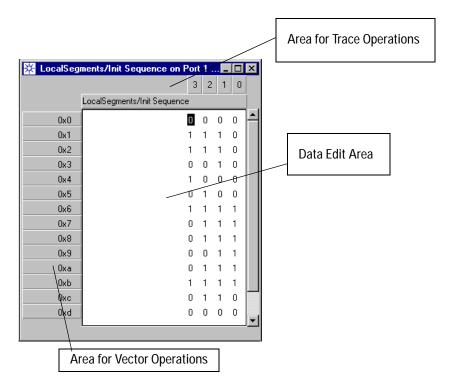

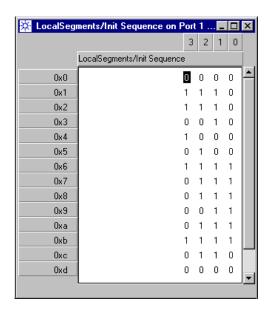

| How to Edit a Memory Segment                   | 325      |

| How to Edit a PRBS/PRWS Segment                | 335      |

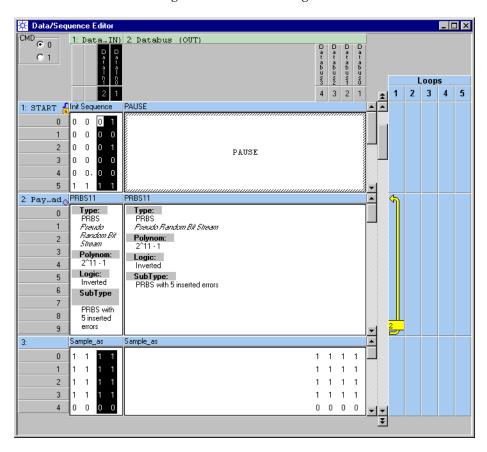

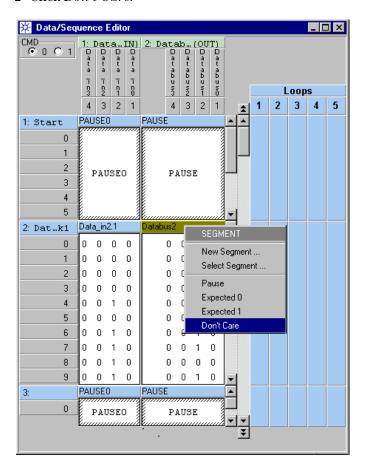

| Using the Data/Sequence Editor                 | 337      |

| How to Start the Data/Sequence Editor          | 338      |

| Contents of the Data/Sequence Editor Window    | 338      |

| How to Customize the Data/Sequence Display     |          |

| How to Change the Width of the Columns         | 340      |

| How to Change the Height of a Block            | 341      |

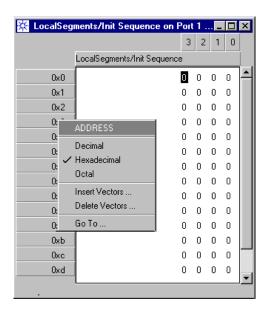

| How to Change the Format of Displayed Address  | es 342   |

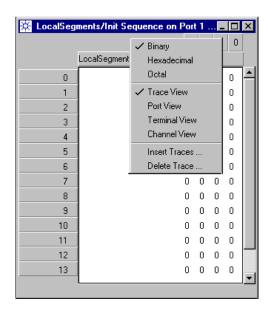

| How to Change the Labels of Displayed Traces   | 342      |

| How to Change the Sequence or Edit Segment     | is 343   |

| How to Change the Sequence Characteristics     | 343      |

| How to Replace a Segment                       | 344      |

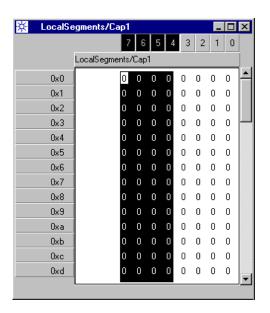

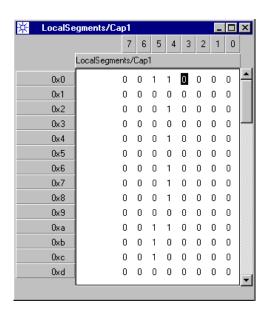

| How to Edit the Contents of a Segment          | 345      |

| Running the Test   |                                                    | 347 |

|--------------------|----------------------------------------------------|-----|

|                    | How to Download the Test Sequence                  | 348 |

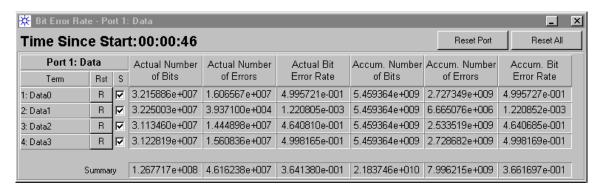

|                    | How to View BER Test Results                       | 349 |

|                    | How to Start/Stop the Test                         | 350 |

| Viewing Generate   | ed and Captured Data                               | 351 |

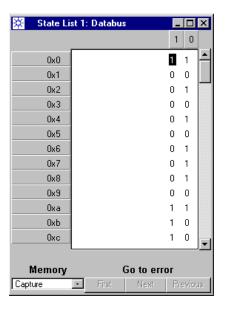

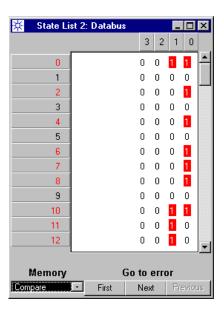

|                    | How to View Captured Test Results                  | 352 |

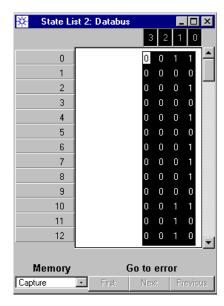

|                    | How to Start the Error State Display               | 352 |

|                    | How to Operate the Error State Display             | 353 |

|                    | How to Transfer Captured Data Into a Segment       | 354 |

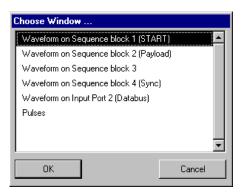

|                    | How to View Waveforms                              | 358 |

|                    | How to Start the Waveform Viewer                   | 358 |

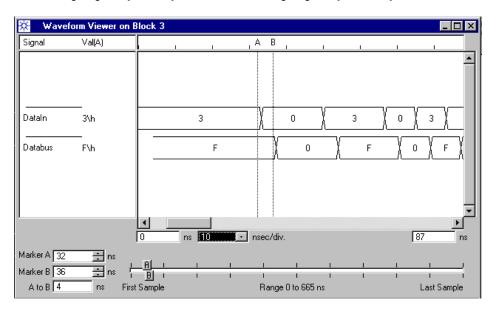

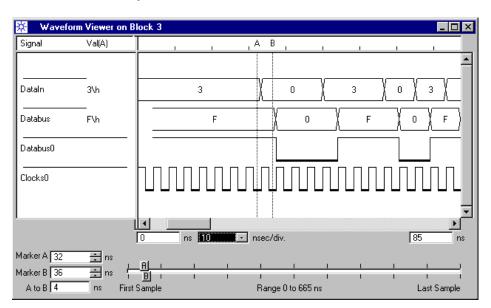

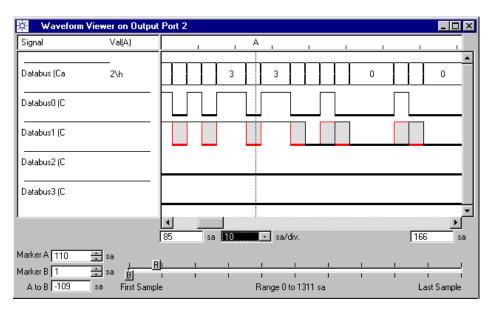

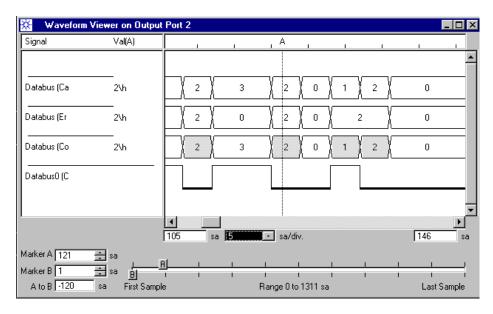

|                    | Description of the Waveform Viewer Display         | 359 |

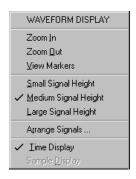

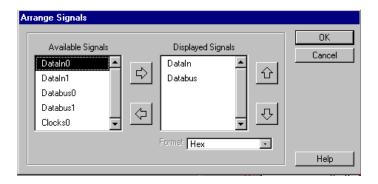

|                    | How to Operate the Waveform Viewer                 | 360 |

| Using Auxiliary Fu | unctions                                           | 365 |

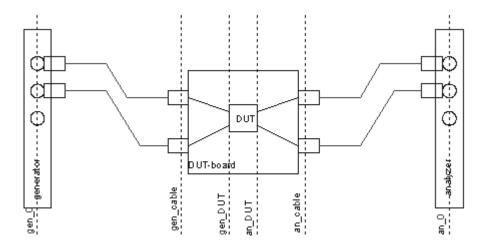

|                    | How to Compensate for Internal and External Delays | 366 |

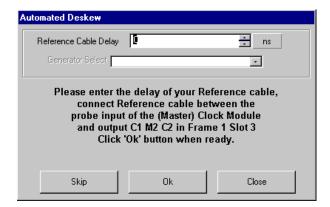

|                    | How to Start the Deskew Editor                     | 368 |

|                    | How to Adjust the Instrument Connectors            | 368 |

|                    | How to Compensate for Cable Delays                 | 370 |

|                    | How to Compensate for Cable and DUT Board Delays   | 373 |

|                    | How to Deskew Optical Connections                  | 376 |

|                    | Prerequisites for Deskewing Optical Connections    | 376 |

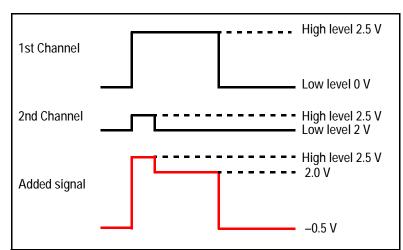

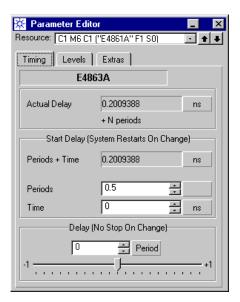

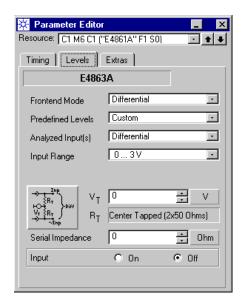

|                    | Zero Adjustment                                    | 376 |

|                    | Cable Deskew                                       | 377 |

|                    | How to Export/Import Settings or Segments          | 380 |

|                    | Export/Import of a Setting                         | 380 |

|                    | Export/Import of Segments                          | 382 |

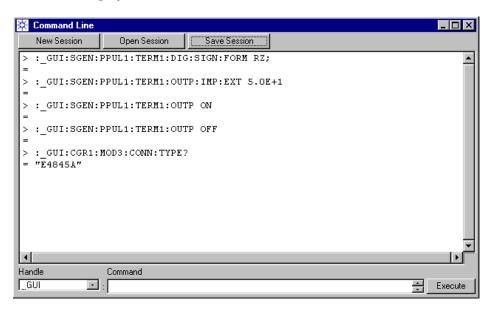

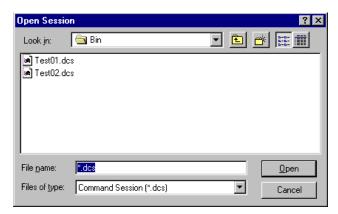

|                    | How to Execute Firmware Commands                   | 384 |

|                    | How to Start the Command Line Editor               | 384 |

|                    | How to Use the Command Line Editor                 | 385 |

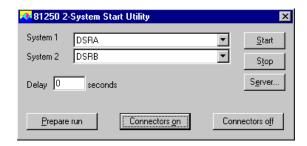

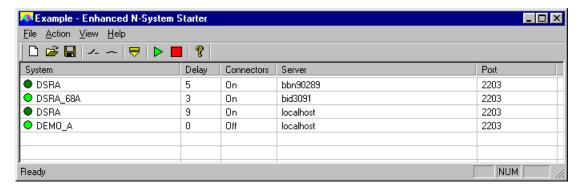

|                    | How to Use the System Starter Utilities            | 387 |

|                    | Using Multiple Systems                             | 387 |

|                    | Using the System Starter for 2 Systems             | 388 |

|                    | Using the System Starter for n Systems             | 389 |

| Appendix A: How Do I ?                                         | 391   |

|----------------------------------------------------------------|-------|

| How Do I Generate a Clock Signal With a Data Module            | ? 392 |

| How Do I Use Events?                                           | 394   |

| How Do I Select Between Two Different Tests?                   | 394   |

| How Do I Set a Trigger on Error?                               | 395   |

| How Do I Allow the DUT to Stabilize?                           | 395   |

| How Can I Return Pass/Fail Information to another Test System? | 396   |

| How Can I Execute Different Tests Within One Sequence?         | 398   |

| How Can I Change all Traces of a Port to Don't Care?           | 399   |

| How Do I Set Up a Multiplexer BER Test?                        | 402   |

| How Do I Use Automatic Sampling Point Adjustment?              | 405   |

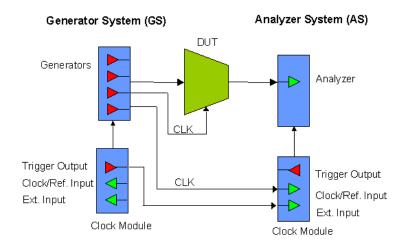

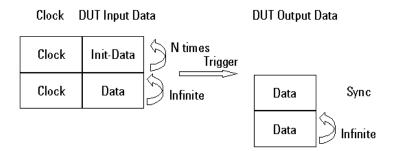

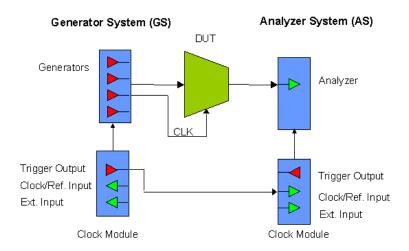

| How Can I Synchronize a MUX Test With Two Systems?             | 405   |

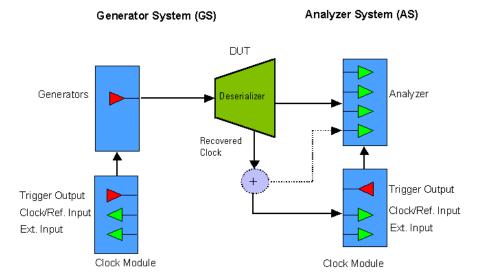

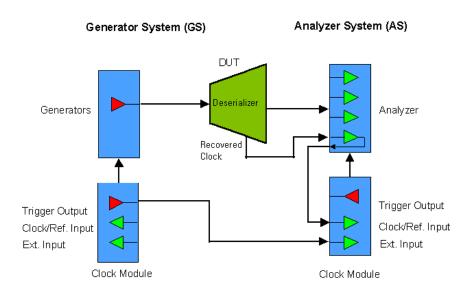

| How Can I Synchronize a DEMUX Test With Two Systems?           | 410   |

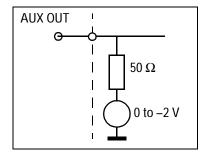

| How Do I Use the AUX OUT of Analyzer Frontends?                | 414   |

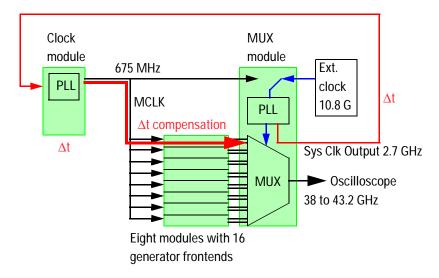

| How Do I Calibrate a 43G Pattern Generator?                    | 415   |

| Appendix B: PRBS/PRWS Data Segments                            | 427   |

| Pure and Distorted PRBS                                        | 428   |

| Variable Mark Density                                          | 429   |

| Extended Zeros/Ones                                            | 430   |

| Error Insertion                                                | 430   |

| Pure and Distorted PRWS                                        | 431   |

| Pure PRWS                                                      | 431   |

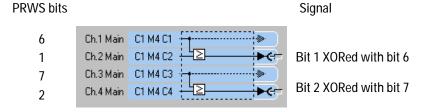

| Distorted PRWS                                                 | 432   |

| Appendix C: Glossary                                           | 433   |

# **About this Guide**

This user guide provides comprehensive information on the hardware and standard user software of the Agilent 81250 Parallel Bit Error Ratio Tester.

This guide does not cover:

- $\bullet \;\; System \; in stall at ion/update$

- System configurations

- Technical specifications

- The Agilent 81250 ParBERT Measurement Software

Information on these topics is available in dedicated manuals.

E-mails You can contact the ParBERT support under the e-mail address parbert\_support@agilent.com.

# Structure of the System User Guide

As the ParBERT System User Guide comprises quite many chapters, you may wish to have some kind of overview to decide how to make optimum use of this document. This first chapter provides that overview.

# **General Structure**

Actually, the information is organized into four sections, though these sections are not explicitly labeled in the manual:

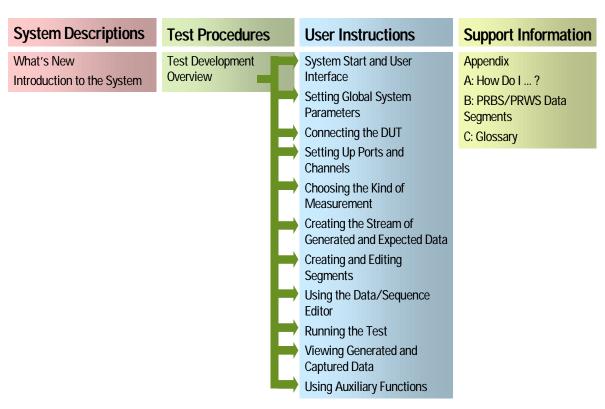

Figure 1 User Guide Structure

The chapter *Test Development Overview* describes the sequence of steps to be performed when developing, executing, and verifying a device test. It points to the corresponding instructions.

# **Contents of the Chapters**

What's New? If you have already been working with the Agilent 81250 Parallel Bit

Error Ratio Tester and received a new software release, you should read this section. It informs you about the changes that have been

made and the enhancements that have been added.

Introduction to the System Newcomers should read this chapter in order to find out what they can

expect from the Agilent 81250 Parallel Bit Error Ratio Tester, what the

hardware components do, and how the system works.

Advanced users will use this chapter as a reference for the terms that

appear on the user interface.

Test Development Overview

This chapter summarizes the steps which are necessary for testing a

device with the Agilent 81250 Parallel Bit Error Ratio Tester—from setup to results. As the system has been designed for ease of use, these

steps can be performed by clicking tool bar icons.

System Start and User Interface You can of course start the system and find out yourself how the user

interface works and how it is operated. The online help will assist you. But you will probably miss a couple of details which could make your

life easier. Such details are discussed in this chapter.

Setting Global System Parameters This and the following chapters provide task-related information. They

are sorted according to the step-by-step procedures stated in the *Test*

Development Overview chapter.

Global system parameters refer to the setup of the clock module.

Setting the test frequency is easy. But if you wish to take advantage of the system's capabilities, you will also need some general information

about the system's timing principles from the Introduction chapter.

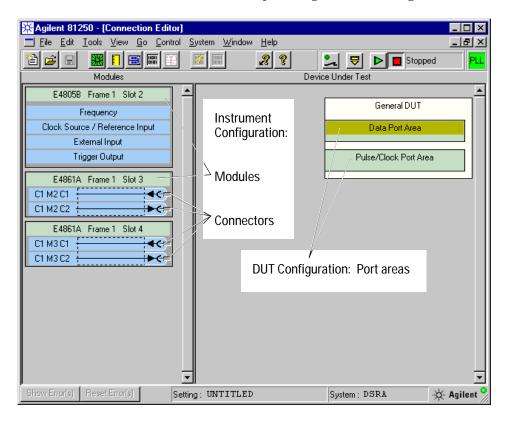

Connecting the DUT This chapter explains how to use the Connection Editor. The

Connection Editor is the first window after starting the Agilent 81250

Parallel Bit Error Ratio Tester User Software.

Setting Up Ports and Channels This chapter explains how to specify the timing, voltages, operating

modes and more of the generator and analyzer frontends.

Choosing the Kind of Measurement The Agilent 81250 Parallel Bit Error Ratio Tester User Software allows

to capture data, to compare received data in real time with expected data, and to measure the bit error rate. This chapter explains the

details.

| Creating | the | <b>Stream</b> | of | Generated | and |

|----------|-----|---------------|----|-----------|-----|

|          |     |               |    |           |     |

**Expected Data**

Testing a device most often requires two data streams—one that is generated, and one that is expected and compared with the DUT output. This chapter explains how these streams can be set up with the Sequence Editor.

To understand this and the following chapters, you will need some basic information about the system's data generation principles from the *Introduction* chapter.

**Creating and Editing Segments**

The data to be sent to or expected from the DUT is organized as data segments. This chapter describes how to create such segments.

Using the Data/Sequence Editor

The Data/Sequence Editor is a very versatile tool which is described in this chapter.

**Running the Test**

This chapter explains how a test is started and stopped.

Viewing Generated and Captured Data

Depending on the kind of measurement, the ParBERT user software offers several kinds of result displays. This chapter explains how to enable and operate these displays.

**Using Auxiliary Functions**

Auxiliary functions like delay compensation, data import/export, or the Command Line Editor are described in this chapter.

Appendix A: How Do I ...?

This appendix provides answers to frequently asked questions. If you need to perform a special test or need a special function or mode of operation, you should consult this chapter before calling the Agilent support.

Appendix B: PRBS/PRWS Data

Segments

This appendix explains the creation and properties of the pseudo random bit/word streams generated or expected by the Agilent 81250 Parallel Bit Error Ratio Tester.

Appendix C: Glossary

All the specific terms used by the user interface are explained in this guide, most of them in the *Introduction* chapter. The glossary in the appendix provides a quick reference.

Index

The alphabetical index register has been prepared to assist you in finding any bit of information as simply and quickly as possible.

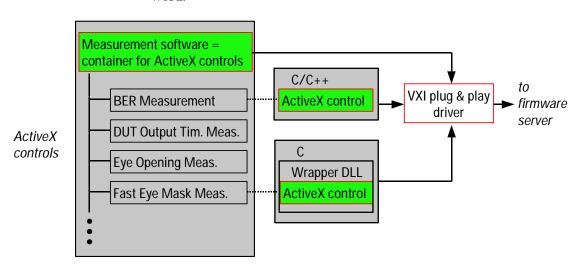

# About the ParBERT Measurement Software

The Measurement Software for the Agilent 81250 Parallel Bit Error Ratio Tester extends the capabilities of the standard system. It provides additional and unequaled features for R&D and production with regard to both test time and precision.

Measurement user interface

The Agilent 81250 Measurement Software has its own user interface, independent from the user interface of the standard user software.

The user interface of the Agilent 81250 Measurement Software consists of a workspace (a window frame) that holds the windows of one or a number of measurements.

Setting

Before you can use the Agilent 81250 Measurement Software you have to create and save a **setting** with the Agilent 81250 User Software.

A setting contains all the system setup information, including the pins of the device to be tested, their connections to the system, the test frequency, the clock source, the timings and levels to be used, the data to be sent or expected, and so on. Once a suitable setting has been stored, the Agilent 81250 User Software does not have to be active for performing the measurements.

**Documentation**

The Agilent 81250 Measurement Software comes with its own manuals.

There is a general guide for all measurements and there are single guides for the individual measurements.

The general guide is the *Agilent 81250 ParBERT Measurement*Software Framework User Guide. The guides for the measurements are named according to the measurements.

# About Special ParBERT Applications

The ParBERT user software provides dedicated tools (utility programs) and manuals for special applications. This is part of Agilent's ongoing effort to offer not only general purpose instruments but also turnkey solutions.

When you receive a new revision of the ParBERT software, it is recommended that you inspect the updated system documentation coming with that revision.

Here are some examples:

Testing SFI-5 devices SFI-5 (SERDES Framer Interface 5) specifies the interface between

the framer and the serializer/deserializer used in transceivers for synchronous optical networks (SONET). For testing such devices,

ParBERT provides special tools and the manual Testing SFI-5 Devices.

Generating SONET/SDH frames ParBERT provides also a tool for generating test data that is formatted

according to the SONET and/or SDH specifications. The related document is the SONET/SDH Frame Generator User Guide.

Testing 10 GbE devices Ten Gigabit/s Ethernet transceivers are specified in an addendum to

the IEEE 802.3 Ethernet specification. ParBERT provides a tool for testing the 10GBASE-R side as well as the XAUI side. The related

document is the manual Testing 10 Gbit/s Ethernet Devices.

Recirculating optical loop tests Recirculating loop tests are a method for simulating long-distance

optical links in a laboratory. ParBERT systems can be used for performing such tests. The manual *Recirculating Optical Loop Tests*

explains how optical loop tests can be set up.

# What's New?

This chapter gives an overview of the most important changes and enhancements of the Agilent 81250 Parallel Bit Error Ratio Tester.

The information is organized as follows:

- "Major Changes in Rev. 5.1" on page 18

- "Major Changes in Rev. 5.0" on page 20

- "Major Changes in Rev. 4.5" on page 23

- "Major Changes in Rev. 4.3" on page 26

- "Major Changes in Rev. 4.2" on page 27

- "Major Changes in Rev. 4.1" on page 30

- "Major Changes in Rev. 4.0" on page 33

# Major Changes in Rev. 5.1

The focus of this revision is on:

- · New optical data analyzer module

- New tool for generating VSR4-formatted data segments

- Application manual for setting up recirculating optical loop tests

- Special support for programming ParBERT systems via the LAN

### **New Data Analyzer Module**

The new module can receive and analyze optical as well as electrical signals at data rates between 21 Mbit/s and 3.35 Gbit/s.

E4811A 3.35 Gbit/s data analyzer module

The E4811A data analyzer module has one channel. It includes an optical-to-electrical (O/E) converter and an electrical data analyzer. It is calibrated for 850 nm wavelength.

The O/E converter includes a sensor and a comparator. External electrical components like filters can be inserted between the sensor and the comparator. The O/E converter provides a differential signal to the data analyzer.

Benefits

This module makes it possible to test optical data transmitters without external O/E converters. In combination with the available E4810A data generator module, you can now test both sides of optical transceivers directly with ParBERT.

Such measurements are fully supported by the ParBERT Measurement Software.

For details see "Modules" on page 43.

# **Updated ParBERT Product Structure**

The following table summarizes the presently supported hardware components and system configurations. The table is sorted according to frequency requirements.

You can identify the available modules and fitting frontends. Note that for data rates above 2.7 Gbit/s the high performance clock module E4808A is required.

| Max. data rate           |            | Generator         | Analyzer     | Clock module      | Comment                                                                              |

|--------------------------|------------|-------------------|--------------|-------------------|--------------------------------------------------------------------------------------|

| 45 Gbit/s                | Modules:   | E4868B MUX        | E4869B DEMUX | E4808A            | ParBERT 43/45G special—comes with 8 data generator/analyzer modules                  |

| 10.8 Gbit/s              | Modules:   | E4866A            | E4867A       | E4808A            | No frontends—one chan-<br>nel per module                                             |

|                          |            | N4868A            |              |                   | Optional 10.8 GHz booster<br>module; one channel stan-<br>dard, 2nd channel optional |

| 3.35 Gbit/s              | Modules:   | E4810A            | E4811A       | E4808A            | One channel per module                                                               |

| optical                  |            |                   |              |                   | Both modules can also be used for generating/analyzing electrical signals            |

| 3.35 Gbit/s              | Modules:   | E4861B            | E4861B       | E4808A            | Two frontends (channels) per module                                                  |

|                          | Frontends: | E4862B            | E4863B       |                   |                                                                                      |

| 2.7 Gbit/s               | Modules:   | E4861A            | E4861A       | E4808A,<br>E4805B | Two frontends per module                                                             |

|                          | Frontends: | E4862A            | E4863A       |                   |                                                                                      |

| 1.65 Gbit/s <sup>a</sup> | Modules:   | E4861A            | E4861A       | E4808A,<br>E4805B | Two frontends per module                                                             |

|                          | Frontends: | E4864A            | E4865A       |                   |                                                                                      |

| 675 Mbit/s               | Modules:   | E4832A            | E4832A       | E4808A,<br>E4805B | Four frontends per module                                                            |

|                          | Frontends: | E4838A,<br>E4843A | E4835A       |                   | E4835A means 2 frontends                                                             |

Table 1 Supported Modules and Frontends

For details please refer to the  $Agilent\ 81250\ ParBERT\ Technical\ Specifications.$

#### **VSR4 Frame Generator**

The VSR4 Frame Generator is a tool that allows you to generate ParBERT data segments that hold test data formatted according to the implementation agreement OIF-VSR4-01.0.

The payload can be pure PRWS (pseudo random data) or data formatted as SONET frames (generated with the SONET/SDH Frame Generator).

<sup>&</sup>lt;sup>a</sup> E4864A and E4865A frontends delivered before February, 2002, are confined to 1.35 Gbit/s.

This supports the testing of components that conform to the VSR OC-192/STM-64 interface specifications.

The tool comes with online help and the manual VSR4 Frame Generator.

### **Support of Recirculating Optical Loop Tests**

Recirculating loop tests are a method for simulating long-distance optical links in a laboratory. ParBERT systems can be used for performing such tests.

New Manual "Recirculating Optical Loop Tests"

The manual *Recirculating Optical Loop Tests* explains how optical loop tests can be set up with ParBERT.

# Support for Programming ParBERT Systems via the LAN

The ParBERT software package includes libraries that provide multiple ways for users as well as for test and measurement applications to control and program ParBERT via the LAN.

New Manual "Agilent 81250 ParBERT LAN Programming Guide" The *LAN Programming Guide* provides a practical guide to programming ParBERT via the LAN using Agilent IO Libraries, Telnet, Socket connections, or all of them. The theory can be found in the manuals enclosed in the Agilent IO Libraries install package.

# Major Changes in Rev. 5.0

The highlights of this revision are:

- Optical data generator module

- New tool for testing 10 Gigabit/s Ethernet devices

- Enhancements of the ParBERT user interface

- Enhancements of the ParBERT Measurement Software

- A new method for aligning analyzer bit recognition to the incoming data

- · Remote check of connector status

#### **New Data Generator Module**

The new module can generate optical as well as electrical signals at data rates between 21 Mbit/s and 3.35 Gbit/s. With 850 nm wavelength (option 001), the optical interface is in the short distance range.

E4810A 3.35 Gbit/s data generator module

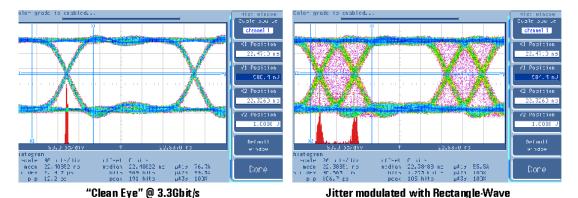

The E4810A data generator module has one channel. It includes an electrical signal generator and an electrical-to-optical (E/O) converter. It features variable crossing and variable jitter. Jitter distribution can be controlled by an external voltage source.

**Benefits**

This module can be used for stimulating optical receivers. In combination with the available electrical analyzers (like the E4863B frontends), you can stimulate optical receivers and measure the electrical response.

Such measurements are fully supported by the ParBERT Measurement Software.

For details see "Modules" on page 43.

#### 10Gb Ethernet Tool

The 10Gb Ethernet Tool supports tests of 10 Gbit/s Ethernet (10GbE) transceiver devices that conform to the 10GBASE-R and XAUI specifications as defined in the IEEE 802.3 addendum for 10GbE (IEEE 802.3ae).

Testing Xenpak devices

Such devices are standardized and developed, for example, by the members of the Xenpak authority.

The 10Gb Ethernet Tool allows you to generate ParBERT data segments holding 10GbE-formatted data as well as recommended test patterns. It enables you to execute 10GbE tests. It can automatically upload and post-process captured data.

New Manual "Testing 10 Gbit/s Ethernet Devices" The information on 10GbE tests has been combined in the new application manual *Testing 10 Gbit/s Ethernet Devices*.

#### **Enhancements of the ParBERT User Interface**

The most important enhancement refers to the frequency setup.

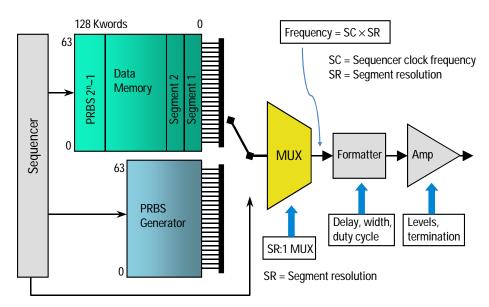

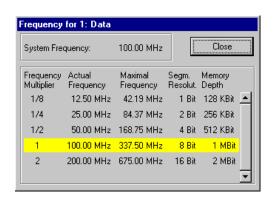

The *segment resolution* is the length of a word in the memory of one or several ParBERT modules. Since the memory is organized to hold approximately 128 Kwords, the word length defines the available amount of memory.

Depending on the type of module and the chosen data rate, the segment resolution required for a particular port or channel can vary between one and 256 bits.

Setting the optimum segment resolution requires some insight into the way ParBERT generates bit rates (described in "Frequency Multiplier and Segment Resolution" on page 68).

#### **Automatic calculation**

To assist users who do not wish to dig into those details, the Parameter Editor for the clock module now allows you to choose between manual and automatic mode.

In automatic mode, the program automatically calculates a suitable segment resolution.

For details see "How to Set the General System Frequency" on page 178.

#### **Enhancements of the ParBERT Measurement Software**

The ParBERT Measurement Software includes the DUT Output Timing/Jitter Measurement.

Up till now, the jitter evaluation has only reported the total jitter (TJ).

#### DJ/RJ separation

New setup parameters and calculations have been added measurement to separate between random jitter (RJ) and deterministic jitter (DJ).

For details, please refer to the documentation of the Agilent 81250 ParBERT Measurement Software.

# **Fast Bit Synchronization**

If pure PRxS data is used, Fast Bit Synchronization is a new way to synchronize analyzers to the incoming data stream.

This method is fast, because it needs only few data bits and does not optimize the sampling delay.

Fast Bit Synchronization does not replace the current synchronization methods. It does not report the final delay.

Fast Bit Synchronization has been implemented to support first of all "Recirculating Loop Tests" for optical fiber connections.

For details see "Fast Bit Synchronization" on page 97.

### **Remote Check of Connector Status**

The frontends have built-in protection circuits which automatically disconnect a frontend if an attempt is made to operate the frontend under intolerable conditions.

If this happens, the user interface is neither informed nor updated. In case of a problem, it is therefore recommended to inspect the green LEDs above the frontend connectors. They indicate the physical connection status.

A new command has been implemented that allows remote programs to check the connector status.

For details see the System Programming Guide and SCPI Reference.

# Major Changes in Rev. 4.5

This revision of the Agilent 81250 software provides:

- Extended support for testing SFI-5 SERDES devices

- · Support of the enhanced ParBERT 43G systems

- Support for the new N4868A 10.8 GHz booster module

- Enhancements of the ParBERT Measurement Software

# **Enhanced Support for Testing SFI-5 Devices**

The tools for testing SFI-5 SERDES devices (SERializers/DESerializers) are the SFI-5 Frame Generator utility and the SFI-5 Post Processing Tool.

The SFI-5 Frame Generator utility is used for generating SFI-5 formatted data segments, and the SFI-5 Post Processing Tool for analyzing the captured data.

SFI5 Data Segment

For E4861B 3.35 Gbit/s data generator/analyzer modules, a new type of data segment is provided. It specifies pure PRWS data that is formatted according to the SFI-5 standard and includes the DSC signal.

The advantage is that such a segment does not have to be generated on the ParBERT controller and downloaded—the E4861B modules generate the data by themselves, the random data as well as the deskew channel data. This saves not only test time and data memory, but allows the use of high-order PRxS polynomials up to  $2^{31}$ –1.

New Manual "Testing SFI-5 Devices"

To reflect Agilent's ongoing effort to provide not only general purpose instruments but also turnkey solutions, the information on SFI-5 has been combined in the new application manual *Testing SFI-5 Devices*.

### **Enhanced ParBERT 43G Systems**

The MUX/DEMUX modules of the high-speed ParBERT 43G systems have been enhanced. New ParBERT 43G bundles include these modules.

New bundles

You can now choose between four ParBERT 43/45G bundles. They contain either 2.7 Gbit/s or 3.35 Gbit/s data modules and frontends.

For details see "ParBERT 43/45G Components" on page 108.

New E4868B MUX / E4869B DEMUX modules

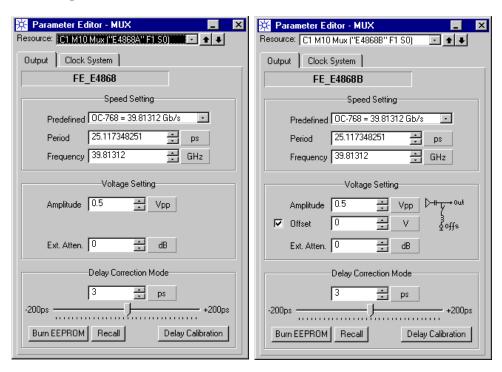

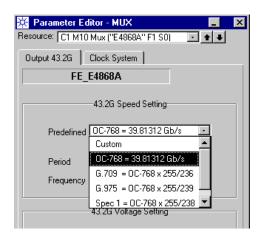

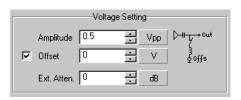

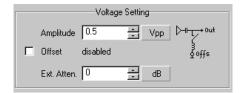

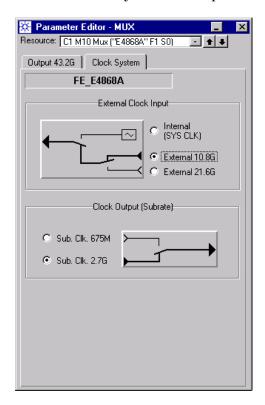

The B-versions of the MUX/DEMUX modules provide additional and extended features that can be controlled from the user interface.

The E4868B MUX module allows you to add an offset voltage to its output. The E4869B DEMUX module allows you to tune its sampling delay manually.

Both modules support full segment resolution and hence memory capacity of the 3.35 Gbit/s data generators/analyzers. A system equipped with these modules can exceed frequencies of 43.2 Gbit/s.

For details see "How to Set Up a 43G MUX/DEMUX Module" on page 210.

#### **New Module**

New N4868A 10.8 GHz booster module

The N4868A 10.8 GHz booster module is an add-on to the E4866A 10.8 Gbit/s data generator modules. It contains two or four signal conditioners/amplifiers for applications that require optimum signal quality.

The N4868A 10.8 GHz booster module improves the slew rates and hence reduces the transition times of the generated signals considerably.

This module can be connected between the E4866A 10.8 Gbit/s data generator module and the DUT. Its input is the differential output of one or two generator modules.

You can also use the high-speed amplifiers in single-ended mode. In this mode, you can operate each amplifier separately. For example, you can connect two 10.8 Gbit/s generators—both set to single-ended operation—and amplify two separate signals.

The software supports individual parameter settings for each of the amplifiers. For details see "N4868A Module" on page 51.

### **New Output Level Measurement**

A new measurement type has been added to the ParBERT Measurement Software. The Output Level measurement allows you to determine the bit error rate at varying receiver thresholds.

This measurement can be used for investigating the behavior of the DUT. A direct result is the determination of the optimum analyzer threshold level for receiving data from the DUT with maximum confidence.

Variable Decision Threshold Method

The method used by this measurement is commonly known as *Variable Decision Threshold Method*. It provides a "vertical" analysis of the eye opening seen by the receiver(s). This method allows you to determine more than just the actual levels.

The Output Level measurement calculates also the Q-factor (a measure that describes the quality of the received signal) and derived values. These results can assist you in characterizing the device. They can also enable you to predict very low bit error rates that would take a long time to measure.

For details please refer to the documentation of the Agilent 81250 ParBERT Measurement Software.

# Major Changes in Rev. 4.3

This revision of the Agilent 81250 user software provides first of all enhancements and extended support of ParBERT 43G systems.

## ParBERT 43/45G Systems with 3.35 GHz Modules

Up to now, the ParBERT 43G systems were restricted to E4861A 2.7 Gbit/s data generator/analyzer modules, equipped with E4862A generator or E4863A analyzer frontends.

From now on, ParBERT 43/45G systems can also be based on E4861B 3.35 Gbit/s data generator/analyzer modules.

A ParBERT 45G pattern generator system would use eight E4861B data generator/analyzer modules with 16 E4862B generator frontends connected to the MUX module.

A ParBERT 45G error detector system would use eight E4861B data generator/analyzer modules with 16 E4863B analyzer frontends connected to the DEMUX module.

#### **Software Enhancements**

New size of the main window

When you start this revision of the ParBERT user software for the first time, you will find that the main window has been enlarged. This supports the display of the ParBERT 43G windows, especially the Connection Editor.

This requires a minimum display resolution of  $800 \times 600$  pixels.

New predefined level

A new predefined signal level has been added. It is called CML and is meant (and automatically set) for channels connected to E4868 MUX or E4869 DEMUX modules.

**DEMUX** rewiring

Depending on the complexity of the demultiplexer and the chosen rewiring algorithm, DEMUX rewiring can take some time. It now runs with twice the speed as before. In addition, the *Rewiring* phase is now indicated by the side of the Run/Stop buttons, like all the other phases of a test.

# Major Changes in Rev. 4.2

Revision 4.2 of the Agilent 81250 user software supports the ParBERT module and frontends for data generation and analysis at rates from 21 Mbit/s up to 3.35 Gbit/s.

In addition, the frontends E4864A and E4865A have been enhanced.

## New Data Generator/Analyzer Module

The new module is:

• E4861B 3.35 Gbit/s data generator/analyzer module

Like the E4861A 2.7 Gbit/s data generator/analyzer module, this new module houses two frontends. Generator and analyzer frontends can be mixed.

## New Data Generator/Analyzer Frontends

The new frontends that can be installed into the E4861B data generator/analyzer module are:

- E4862B 3.35 Gbit/s data generator frontend

- E4863B 3.35 Gbit/s data analyzer frontend

Both frontends have a maximum data memory capacity of 16 Mbit.

E4862B data generator

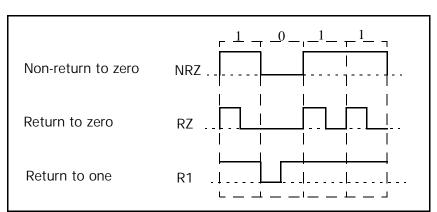

In addition to the extended frequency range and memory, the E4862B  $3.35~\rm Gbit/s$  data generator frontend has features that are not available for the other generators:

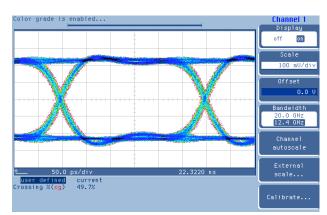

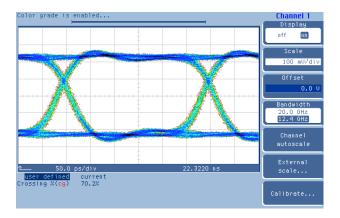

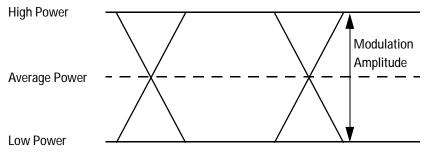

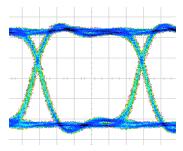

· Variable signal crossing

Standard data generators produce a signal where the crossing point is at  $50\,\%$  of the amplitude. For the E4862B data generator frontend, the crossing point of NRZ signals can be freely adjusted between  $30\,\%$  and  $70\,\%$  of the signal amplitude. This allows you to generate signals with non-symmetrical eye openings.

For details see "How to Set Generator Timing Parameters" on page 229.

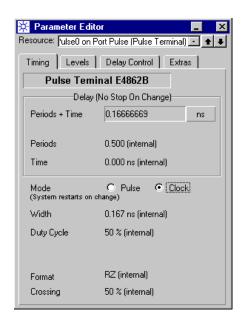

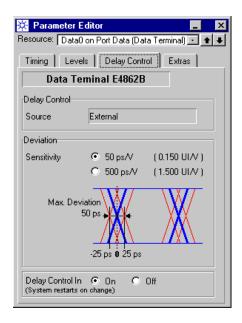

Voltage controlled delay

The E4862B data generator frontend has an input connector. This connector allows you to connect a voltage that controls the signal delay. The linear voltage range is  $\pm 0.5$  V. By varying this voltage, it is possible to generate a signal with jitter of arbitrary distribution.

Frequencies from DC to 200 MHz are supported for the delay control.

For details see "How to Use the Variable Delay (FEs of Type E4862B Only)" on page 240.

· Precision clock generation

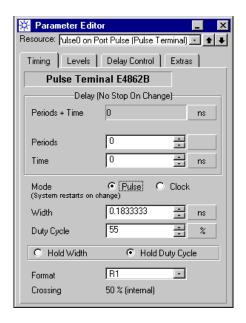

When the E4862B data generator is connected to a pulse port, it produces a clock signal, like all the generators. For this frontend, you can now choose between *Pulse Mode* and *Clock Mode*.

In *Pulse Mode*, you can specify a start delay, the data format, and also width or duty cycle. In *Clock Mode*, a precision clock signal is generated, with fixed delay, 50 % duty cycle, and very low jitter.

For details see "How to Set Generator Timing Parameters" on page 229.

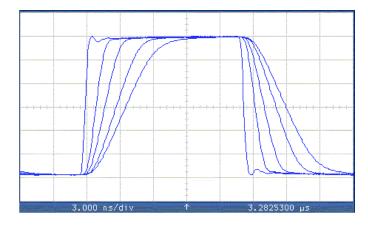

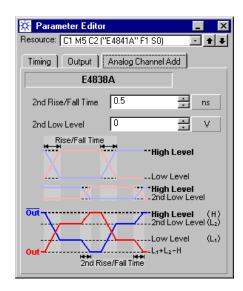

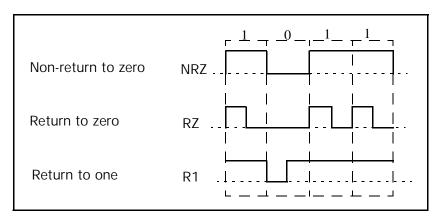

· RZ and R1 data formats

The E4862B data generator supports not only the NRZ data format, like the E4862A data generator frontend does, but also the RZ and R1 data formats.

E4863B data analyzer

The E4863B 3.35 Gbit/s data analyzer frontend has a higher speed and more memory than the E4863A 2.7 Gbit/s data analyzer.

Apart from this, it has the same capabilities:

- · It captures and analyzes incoming data in real time

- It provides an AUX OUT connector that delivers a recovered clock

- It supports all the measurements provided by the Agilent 81250 Measurement Software

Benefits

With the new module and frontends, the Agilent 81250 Parallel Bit Error Ratio Tester addresses:

- 10 Gigabit Ethernet (10GbE) components, including 10G Ethernet Attachment Unit Interfaces (XAUI,  $4\times3.125$  Gbit/s) as proposed by the Xenpak Multisource Agreement

- MUX / DEMUX components (OC-48)

- $\bullet$  Multiple electrical-to-optical (E/O) and optical-to-electrical (O/E) transceivers (VSR OC-768)

- Cross-point switching components

## **Enhanced Data Generator/Analyzer Frontends**

An E4861A data module can accommodate the frontends E4864A and E4865A. New frontends of this type now cover a wider frequency range:

- $\bullet$  E4864A data generator: Formerly up to 1.35 Gbit/s—now up to 1.65 Gbit/s

- $\bullet$  E4865A data analyzer: Formerly up to 1.35 Gbit/s—now up to 1.65 Gbit/s

If new E4864A or E4865A frontends have been added to your system, it is recommended to check the frontend labels that indicate the maximum frequency. The older frontends remain limited to data rates of  $1.35~\rm Gbit/s$ .

# **Updated ParBERT Product Structure**

The following table summarizes the presently supported hardware components. The table is sorted according to frequency requirements.

| Table 2 S | upported | Modules | and | Frontends |

|-----------|----------|---------|-----|-----------|

|-----------|----------|---------|-----|-----------|

| Max. data rate           |            | Generator      | Analyzer     | Clock module      | Comment                             |

|--------------------------|------------|----------------|--------------|-------------------|-------------------------------------|

| 43.2 Gbit/s              | Modules:   | E4868A MUX     | E4869A DEMUX | E4808A            | ParBERT 43G special                 |

| 10.8 Gbit/s              | Modules:   | E4866A         | E4867A       | E4808A            | No frontends—one module per channel |

| 3.35 Gbit/s              | Modules:   | E4861B         | E4861B       | E4808A            | Two frontends per module            |

|                          | Frontends: | E4862B         | E4863B       |                   |                                     |

| 2.7 Gbit/s               | Modules:   | E4861A         | E4861A       | E4808A,<br>E4805B | Two frontends per module            |

|                          | Frontends: | E4862A         | E4863A       |                   |                                     |

| 1.65 Gbit/s <sup>a</sup> | Modules:   | E4861A         | E4861A       | E4808A,<br>E4805B | Two frontends per module            |

|                          | Frontends: | E4864A         | E4865A       |                   |                                     |

| 675 Mbit/s               | Modules:   | E4832A         | E4832A       | E4808A,<br>E4805B | Four frontends per module           |

|                          | Frontends: | E4838A, E4843A | E4835A       |                   | E4835A means 2 frontends            |

<sup>&</sup>lt;sup>a</sup> E4864A and E4865A frontends delivered before February, 2002, are confined to 1.35 Gbit/s.

For details please refer to the  $Agilent\ 81250\ ParBERT\ Technical\ Specifications.$

#### Software Enhancements

Analyzing a received SFI-5 pattern is not trivial. Before the bit error rate can be measured, the skew between the 16 data lines and the 17th data channel must be considered to ensure that the received PRBS data is valid.

SFI-5 Post Processing Tool

For this purpose, the SFI-5 Post Processing Tool has been developed.

This tool analyzes captured SFI-5 patterns. It determines the skew and calculates the BER not only of the 16 data lines but also of the additional synchronization channel.

The SFI-5 Post Processing Tool comes with its own user interface. This interface allows you to start a test, to inspect the results, and to save the captured data into a data segment. For details see the manual *Testing SFI-5 Devices*.

# Major Changes in Rev. 4.1

Revision 4.1 of the Agilent 81250 user software supports the ParBERT 10.8 Gbit/s data generator/analyzer modules. It provides also enhancements of the Segment Editor and a new way to switch the connectors on and off.

# New Data Generator/Analyzer Modules

The new modules are:

- E4866A 10.8 Gbit/s data generator module

- E4867A 10.8 Gbit/s data analyzer module

These modules are capable of creating or analyzing data streams at 9.5 Gbit/s up to 10.8 Gbit/s.

**Benefits**

You may think of testing a multiplexer component, stimulated by four 2.7 Gbit/s generators or eight 1.35 Gbit/s generators. One single E4867A 10.8 Gbit/s analyzer can measure the serial response. Similarly, a demultiplexer can be stimulated by an E4866A 10.8 Gbit/s data generator and analyzed by four, eight, or 16 lower speed analyzers.

You may also think of high-speed applications. For example, four E4866A data generator modules can be used for stimulating an OC-768 4:1 multiplexer. The serial output of this multiplexer with a data rate around 40 Gbit/s can be analyzed by a ParBERT 43G error detector system.

Using a ParBERT 43G pattern generator system, you can send a serial bit stream of up to 43.2 Gbit/s to an OC-768 demultiplexer component. Using four E4867A data analyzer modules, it is now possible to analyze the parallel output of a 1:4 demultiplexer.

Details

These high-speed modules do not have frontends. Each has one pair of differential connectors which is identified by the software as one connector. For these modules, one channel means one module.

From the user's point of view, this is the only remarkable difference to the lower speed modules. For the connection and parameter setup, the same functions of the Connection Editor and Parameter Editor are used.

Automatic analyzer sampling delay adjustment and all the measurements provided by the Agilent 81250 Measurement Software can be used with the E4867A 10.8 Gbit/s data analyzer modules.

## **Enhancements of the Segment Editor**

For testing a multiplexer, one needs parallel generated and serial expected data. Testing a demultiplexer requires serial generated and parallel expected data. The data contents is the same on both sides—only the data distribution changes.

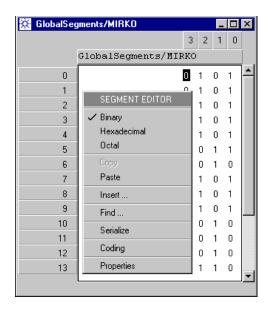

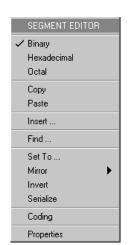

To support the setup of data to be generated and expected for multiplexer and demultiplexer tests, three functions have been added to the Segment Editor, and one has been enhanced.

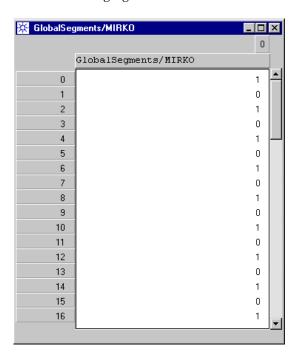

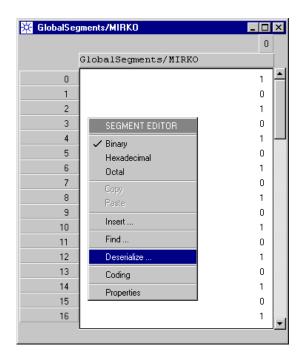

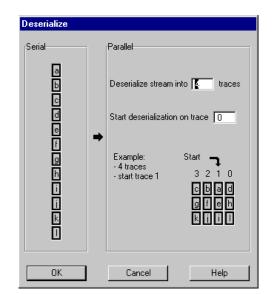

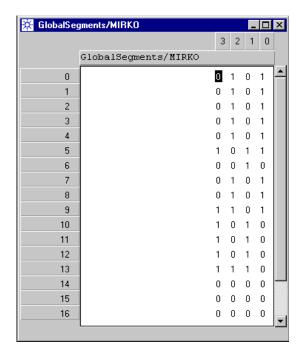

Deserialize

The Deserialize function allows you to convert a serial bit stream to parallel format. This is done in the data segment. A segment holding serial data contains just one trace. With the Deserialize function, this data can be split into an arbitrary number of traces.

This, for example, makes it easy to create the data expected from a demultiplexer. To adapt to the characteristics of the demultiplexer, the function provides several alternatives for sorting the data.

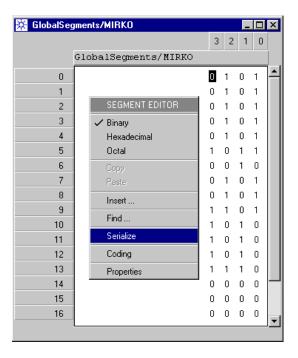

Serialize

This function is the counterpart of the descrialize function. It is used to convert parallel data to serial. A segment holding multiple traces is converted to a serial segment holding one trace.

Again, several alternatives are provided for sorting the data.

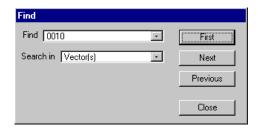

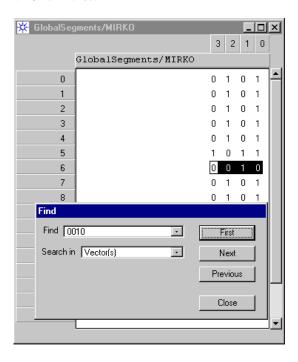

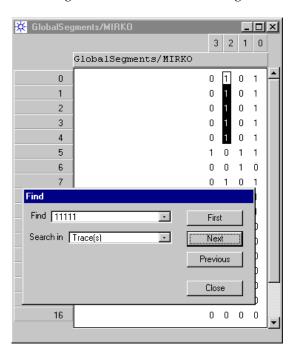

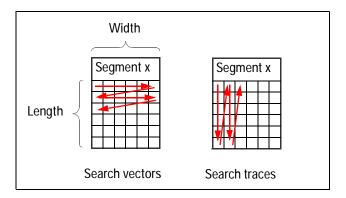

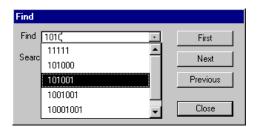

Find Formatted data is generally organized in blocks. Such blocks contain header, control, and payload data. You may wish to pursue the order of these blocks.

This is supported by the Find function. This function allows you to search for a certain bit combination within a segment. You can search for parallel and serial bit patterns.

**Enhanced copy and paste**

When testing n:1 multiplexers or 1:n demultiplexers, you may need separate ParBERT systems on the generating and analyzing sides. This depends on the frequency ratio. Using two ParBERT systems, in turn, means using two user interfaces.

You may, for example, have set up suitable test data for the generator system. But how to transfer that data to the analyzer system, so that it recognizes the expected data?

This is covered by the enhanced copy and paste functions of the Segment Editor.

As soon as the Segment Editors of both user interfaces are open, you can copy and paste memory data from one to the other.

This, combined with the Deserialize/Serialize functions, makes it easy to set up all kinds of multiplexer/demultiplexer tests.

# Switching Connectors ON/OFF

The tool bar of the ParBERT user interface has always had a Connectors Off/On button for disconnecting all the frontends and for re-establishing the previous connections. This was done by switching relays in the frontends.

For frontends with data rates above 675 Gbit/s, this behavior can be changed. It is now possible to specify whether the relays shall be switched or whether the frontends shall be disconnected by grounding.

Especially in a production environment, grounding is a way to increase the lifetime of the ParBERT relays.

# Major Changes in Rev. 4.0

Revision 4 supports not only all common ParBERT configurations but also the *Agilent 81250 ParBERT 43G Systems*. This is accompanied by enhancements of the Agilent 81250 Configuration Tool and the start procedure of the Agilent 81250 user software.

## **Agilent ParBERT 43G Systems**

The Agilent 81250 ParBERT 43G is a solution for generating and analyzing electrical data streams of 38 Gbit/s up to 43.2 Gbit/s.

It allows you to stimulate and analyze 16:1 multiplexers and 1:16 demultiplexers at data rates of 2.7 Gbit/s and 43.2 Gbit/s, according to the OC-768 and SFI-5 (Serdes Framer Interface 5) data range.

It allows you also to determine the bit error rate of serial devices or transmission lines operated at 43.2 Gbit/s. It supports the investigation of FEC devices at 43.01841 Gbit/s including the FEC rate resulting from 255/236 overhead.

The Agilent 81250 ParBERT 43G systems are offered as bundles—one for pattern generation and one for error detection. But it is also possible to upgrade existing systems.

A setup for testing both multiplexers and demultiplexers would use both bundles. The bundles include also the E4808A clock module which is superior to the well-known E4805B clock module.

For details see "ParBERT 43/45G Systems" on page 107.

#### Software Enhancements

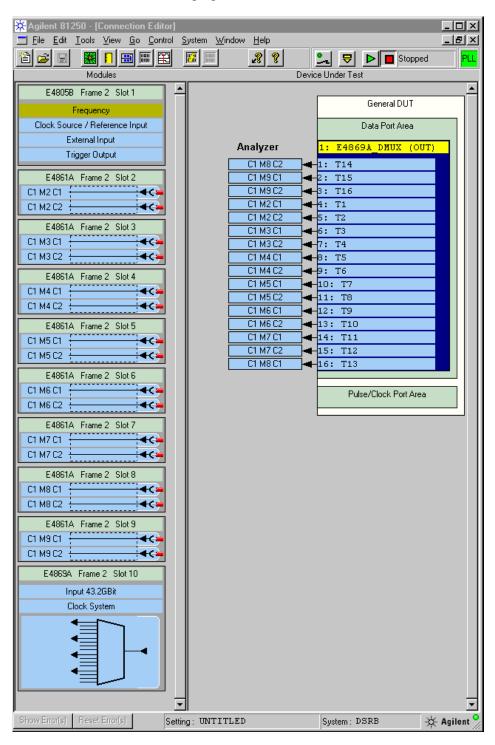

An Agilent 81250 ParBERT 43G system is automatically recognized and the user software comes up with a Connection Editor which is preconfigured.

Using both Agilent 81250 ParBERT 43G bundles means using two ParBERT user interfaces. This is required for independent clock generation and parameter setup. The capability to run more than one user interfaces has always been there.

Support of multiple user interfaces

The Agilent 81250 Configuration Tool and the ParBERT user software now greatly support the use of several user interfaces:

- More than one user interface can be automatically started.

- Every user interface can be individually configured.

The configuration parameters for each user interface include:

Location of the firmware server (local or LAN address), name of the system to be operated, name of the setting to be automatically downloaded to the system.

- Every user interface can easily be switched to operate one of the configured systems.

- Tests can be started an stopped simultaneously on two or more systems.

For details on the System Starters see "How to Use the System Starter Utilities" on page 387.

Data generation for SONET and SFI-5

The Utilities panel provides also the access to two tools used for generating data segments for the ParBERT 43G.

- The SONET SDH Frame Generator generates data that is formatted according to SONET standards (STS 3 to STS 768) or SDH (STM 1 to STM 256). This tool includes its own online help.

- The SFI-5 Frame Generator generates data that is formatted according to SFI-5 standards. For details, see *SFI-5 Frame Generator and the SFI-5 Data Segment* in the manual *Testing SFI-5 Devices*.

External clock sources

If an external clock source is connected to the master clock module, then this source determines the system clock frequency. The software now provides not only the clock multiplier but also a clock divider.

This means, you can, for example, set the system clock frequency to 3/5 of the external clock frequency, or to any other arbitrary value.

PLL lock indicator

When an external clock source is used, the phase locked loop of the master clock module locks onto that source. The PLL lock indicator informs you in case the clock system could not lock or has lost its synchronization.

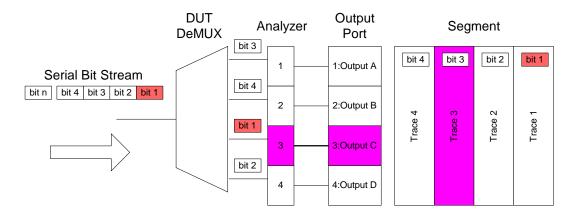

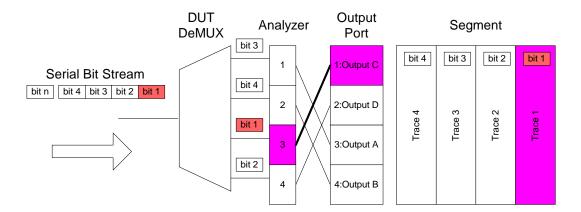

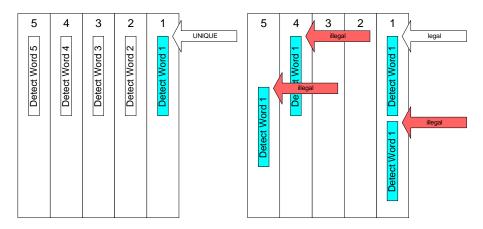

### **Automatic Rewiring of Demultiplexer Terminals**

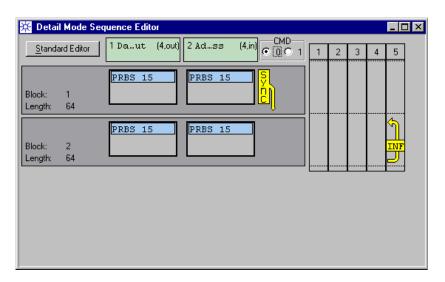

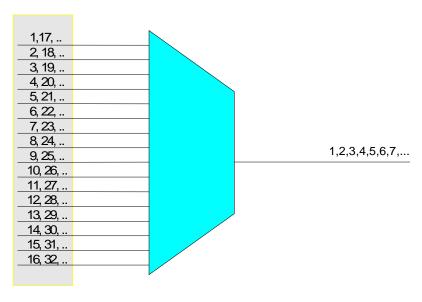

When testing demultiplexers, you apply serial data to one terminal and analyze parallel data from a number of terminals. Pure PRBS and PRWS data are generally well suited for testing demultiplexers.

But if you are using memory-based data, you may encounter the problem that the data from the DUT is correct, but does not start with the first terminal—the one numbered "1". This, however, is required for comparing the received data with the stored data segment. Trace 1 of the segment is expected from the first terminal, trace 2 from the next, etc.

The ParBERT now provides a means to fully automatically check the incoming data and rearrange the sequence of the terminals. As a result, the first terminal is the one that delivers the first bit of every word, the second terminal delivers the second bit, and so on, and the incoming data can be compared with the expected.

For details see "Automatic Rewiring of Demultiplexer Terminals" on page 119.

What's New?

# Introduction to the System

This chapter familiarizes you with the Agilent 81250 Parallel Bit Error Ratio Tester—its components, operating principles, and terms.

The information is organized as follows:

- "System Capabilities" on page 38—a summary of the system's purpose and technical highlights

- "System Components" on page 40—the description of the ParBERT hardware components

- "Operating Principles" on page 58—the philosophy of virtual systems and setup models and its impact on the software structure

- "Timing Principles" on page 66—about clock sources and how the system clock is generated by frequency multiplication

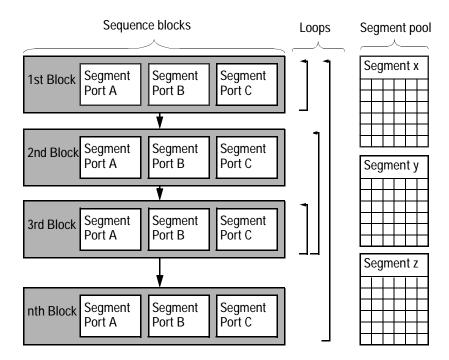

- "Data Generation Principles" on page 78—the characteristics of data sequences, data blocks, and data segments

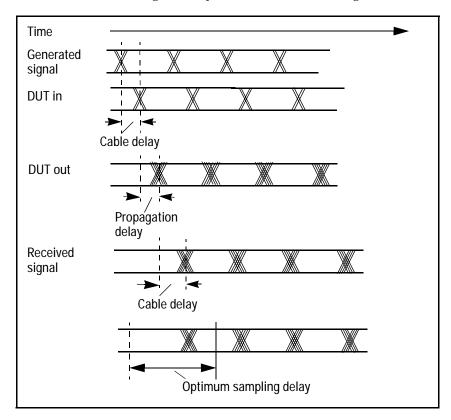

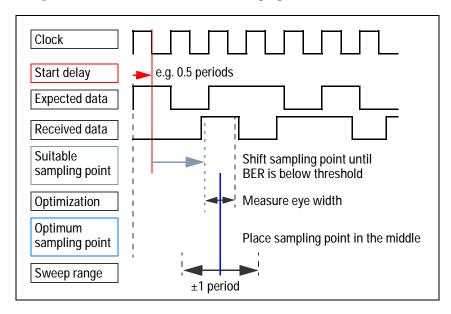

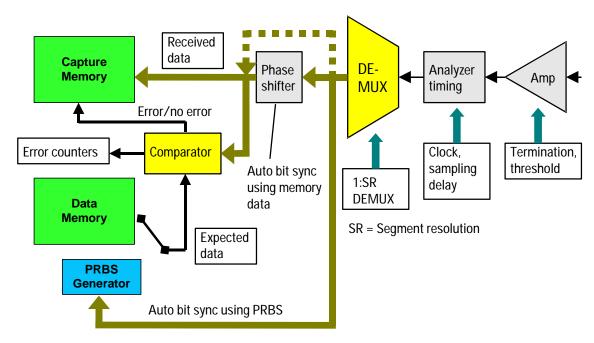

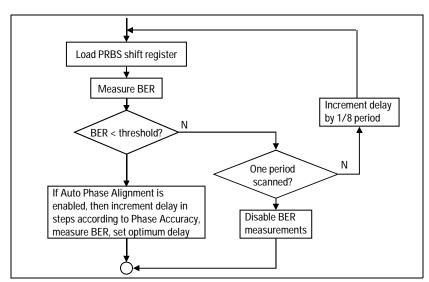

- "Principles of Analyzer Sampling Point Adjustment" on page 87 the three methods for adjusting the analyzer sampling delay

- "Data Capturing and Analysis Principles" on page 101—a description of the four standard functional tests and their result displays

- "Event Handling Principles" on page 104—the explanation of how the system can be influenced by internal and external events

- "ParBERT 43/45G Systems" on page 107—an introduction to the ParBERT 43/45G that allows to create and analyze data streams at rates of 43.2 Gbit/s and higher

- "Automatic Rewiring of Demultiplexer Terminals" on page 119 an overview and more of special features for testing demultiplexers

Multi-Media Guided Tour, Tutorial and Getting Started

As an additional source of information, the Multi-Media Guided Tour, Tutorial and Getting Started provide a comprehensive overview of the Agilent 81250 Parallel Bit Error Ratio Tester. If it has been installed on your system, you will find it in the Windows start menu under *Programs – Agilent 81250 Tutorial*. If not, you can download it from the web through http://www.agilent.com/find/81250demo

# **System Capabilities**

The Agilent 81250 Parallel Bit Error Ratio Tester is first of all meant for testing high-speed data communication equipment (DCE), but can also be used as a multi-purpose digital stimulus/response (DSR) system.

The system can be operated from the graphical user interface or controlled via LAN or GPIB, for example in an automated test rack. It can also control other instruments via GPIB. It has programming interfaces to VEE, C/C++, and others.

# **Verify and Characterize Digital Devices**

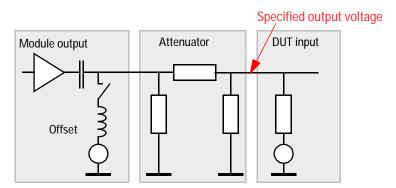

The device under test (DUT) and its test setup are mirrored in the software.

The graphical user interface shows a raw DUT template in the Connection Editor window. In this window it is possible to define groups of signals for the DUT—these groups of signals are called "ports". The DUT template offers two types of ports:

- Data ports are used for data signals such as stimulus data and expected response data.

- Pulse ports are used for pure parametric signals such as clock signals.

All signal parameters can be set up conveniently for a group of pins (a port) as well as separately for single DUT pins (terminals).

The system has data generating and analyzing frontends.

Cable delays and signal skew in the test setup can be compensated by using the deskew feature.

# **Key Features**

The following list summarizes the most important features:

- Stimulus as required, real-time error analysis and margin tests

- Parallel data rates of generator and analyzer channels up to 10.8 Gbit/s

- Serial data rates up to 45 Gbit/s (ParBERT 43/45G)

- Up to 32 Mbit data memory per channel

- Up to 128 generator/analyzer channels at 675 Mbit/s. Up to 64 channels at 1.35, 2.7, or 3.35 Gbit/s. Up to 32 channels at 10.8 Gbit/s

- 2 ps timing resolution

- Pattern formats NRZ, DNRZ, RZ, R1

- Pseudo random bit and word streams (PRBS/PRWS) up to  $2^{15}$ –1 plus  $2^{23}$ –1 and  $2^{31}$ –1

- Automatic analyzer sampling delay adjustment

- Sequencing with up to five loop levels (nested loops)

- Variable delay, width, transition times, voltage levels—individually adjustable for each frontend

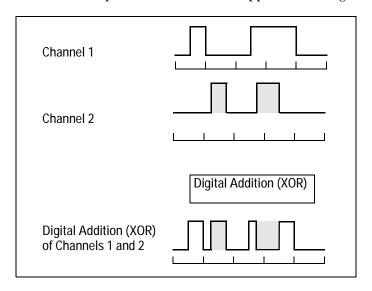

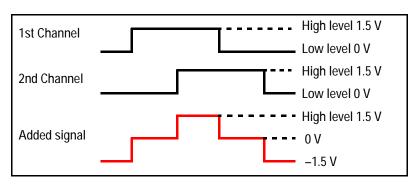

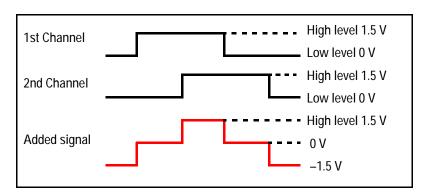

- Logical XOR addition of two or four 675 MHz generator channels

- Analog voltage addition of two 675 MHz generator channels

- Semi-automatic signal delay compensation (deskew)

- Event recognition and reactions upon events

- Tabular and graphical result presentation

- Automated measurements based on measuring the bit error rate at many points in time and voltage: Eye Opening, Fast Eye Mask, DUT Output Timing/Jitter.

- Pass/fail measurements

- Modular hardware structure-mix of low and high-speed channels

- · Frontends for differential and low voltage signals

- Comprehensive support for testing multiplexers/demultiplexers—multiple frequencies, internal and external clocks, DEMUX rewiring, data deserialize and serialize functions

- Comprehensive support for testing optical transceivers—optical signal generators/analyzers; tools for creating formatted generated and expected data

For details please refer to the Agilent 81250 Technical Specifications.

# **System Components**

The Agilent 81250 Parallel Bit Error Ratio Tester is available in many configurations.

Standard configurations include:

- "Mainframes and Controllers" on page 40—the controller can be an external PC or workstation, or a 2-slot VXI module embedded into the mainframe

- "Modules" on page 43—a system consists of at least one clock module and one or several data generator/analyzer modules

- *"Frontends"* on page 53—frontends generate or receive signals. They are plugged into data generator/analyzer modules

- "Trigger Pod" on page 55—a special device that allows to recognize external events

- NOTE This section describes the basic components. For information on the ParBERT 43/45G systems please refer to "ParBERT 43/45G Systems" on page 107.

# **Mainframes and Controllers**

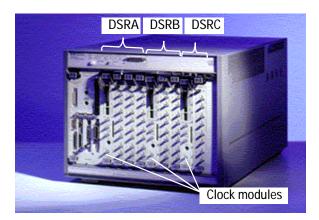

An Agilent 81250 Parallel Bit Error Ratio Tester consists of a VXI mainframe, a controller, and modules plugged into the mainframe.

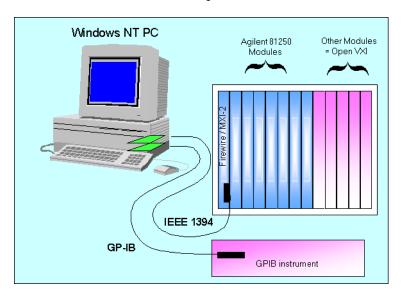

Figure 2 E4860A System Configuration

#### **Mainframes**

13-slot Mainframe

The standard mainframe is the E4803A VXI mainframe with 13 VXI slots.

Figure 3 E4803A VXI Mainframe with Embedded Controller and Modules

Up to two expander frames can be added. The first E4848B expander frame consists of an E8403A mainframe, two E1482B VXI bus extender modules, and connection cables.

The VXI bus extender modules require one slot in both the basic and the added frame. A second expander frame needs only one E1482B VXI bus extender module.

If an external controller is used (see "Controller Options" on page 41), then the E8491B IEEE 1394 PC link to VXI replaces the VXI bus extender modules.

## **Controller Options**

Two options are available for controlling the system:

**External ParBERT Controller**

• The E8491B IEEE 1394 PC link to VXI (opt. #013)

This option allows to use an external PC running under Windows NT or Windows 2000 as the system controller. The option includes a PCI board to be installed in the computer, a 1-slot VXI module to be installed in the mainframe, and all required software.

Opt. #013 leaves 12 mainframe slots for modules.

**Embedded ParBERT Controller**

The built-in 2-slot VXI controller E9850A (opt. #012)

This controller is a VXI module that includes harddisk, diskette drive, a serial and a parallel interface, SCSI controller, GPIB and LAN interface. Operating system and ParBERT software are already installed.

Opt. #012 leaves 11 mainframe slots for modules.

Opt. #012 requires a monitor, keyboard and mouse (supplied with Opt. #010).

#### **Open VXI Configurations**

The Agilent 81200 Data Generator/Analyzer Platform also supports Open VXI configurations. Open VXI enables you to set up your test equipment as compact as required.

As long as free slots are available, VXI modules of other systems can be plugged into the Agilent 81250 mainframe. You need only take care that the Agilent 81250 modules start from the leftmost slot and remain in contiguous slots. Additional software can be installed on the built-in harddisk or the external PC to operate these modules.

Figure 4 IEEE 1394 PC Link and Open VXI Configuration

For details please refer to the *Agilent 81250 Installation Guide* (available as PDF) and the *Configuration Guide*.

Frontends determine

## **Modules**

Clock Module

An Agilent 81250 Parallel Bit Error Ratio Tester is comprised of at least one clock module and one data generator/analyzer module.

Data Modules

# generates the system clock and distributes the clock to the Data Modules - signal generation/ analysis capabilities - speed of channels - type (generator/analyzer) - speed of channels

Figure 5 Modules and Frontends

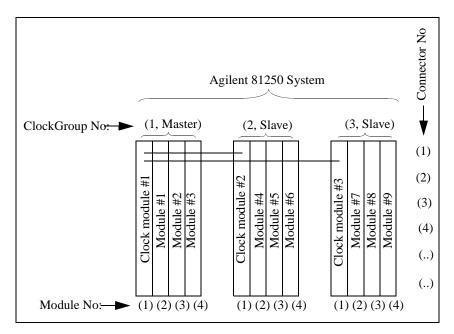

#### **Clock Modules**

The master clock module generates the system clock and synchronizes all data generator and analyzer channels of a system.

The master clock module provides the sequencing capability of a system and can use either its internal synthesized clock source or an external clock source. The internal clock synthesis can be locked to a common frequency standard using the PLL reference input.

The following clock modules are supported:

E4805B Clock Module

• E4805B Clock Module

This module synchronizes up to 11 data analyzer/generator modules. It can additionally control up to two slave clock modules. An expander frame requires a slave clock module.

E4805B Central Clock Module

Clock outputs for modules

Clock for Expander Frame

E4848B

Clock/Ref. Input

External input

Trigger output

Deskew Probe

A deskew probe can be connected and the Agilent 81200 Trigger Pod can be attached to the master clock module.

Figure 6 E4805B Clock Module

The E4805B clock module permits the use of up to 5 loop levels within generated data sequences.

It is also possible to install two or more master clock modules in one mainframe. This results in mutually independent ParBERT systems that share only the housing (see also "Virtual Systems" on page 58).

E4808A Clock Module

• E4808A High Performance Clock Module

This clock module has the same properties as the E4805B clock module, but superior jitter and noise characteristics.

The E4808A clock module has to be used in all ParBERT systems that generate/analyze signals at rates above 2.7 GHz.

### Data Generator/Analyzer Modules

Some data generator/analyzer modules have slots for two or four replaceable frontends.

There are frontends for generating and sourcing signals to the DUT and others for capturing and analyzing signals from the DUT.

Any combination of generator and analyzer frontends within a module is possible. However, it is generally recommended to install the generator and analyzer frontends in separate modules. This supports the concept of grouping output and input signals into "ports" and generating or expecting pseudo random word stream signals (PRWS).

NOTE There are also specific generator modules and analyzer modules. Such modules have no frontends that can be replaced.

The following data generator/analyzer modules are used:

E4832A Module

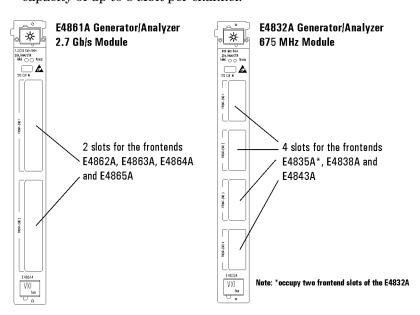

E4832A Data Generator/Analyzer Module (up to 675 MHz):

This module provides four slots for four generator and/or analyzer frontends.

The E4832A module has a memory capacity of up to 2 Mbit per channel. It supports tests and measurements at data rates up to 675 Gbit/s.

E4861A Module

• E4861A Data Generator/Analyzer Module (up to 2.7 GHz):

This module provides two slots for two frontends with maximum data rates of up to 1.65 Gbit/s or 2.7 Gbit/s. It provides a memory capacity of up to 8 Mbit per channel.

Figure 7 E4832A/E4861A Data Generator/Analyzer Modules

NOTE Your system may include older E4832A/E4861A data generator/analyzer modules, marked for frequencies of 1.33/2.67 GHz or 667 MHz. If this is the case, the achievable data rates are limited by the older modules.

#### E4861B Module

E4861B Data Generator/Analyzer Module (up to 3.35 GHz):

This module looks like the E4861A module. It provides two slots for two frontends with maximum data rates of up to 3.35 Gbit/s.

Compared with the E4861A module, it has a much wider frequency range and twice the memory capacity.

E4861B modules must only be used in conjunction with an E4808A clock module.

#### E4810A/E4811A Modules

- These modules are capable of generating or analyzing electrical or optical data streams at 21 Mbit/s up to 3.35 Gbit/s. They are:

- E4810A 3.35 GHz electrical-optical data generator module

- E4811A 3.35 GHz optical-electrical data analyzer module

They can only be used in conjunction with an E4808A clock module.

Figure 8 E4810A/E4811A Data Generator/Analyzer Modules

These modules have no replaceable frontends. For these modules, one  $\it channel$  means one module.

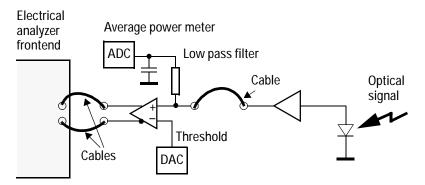

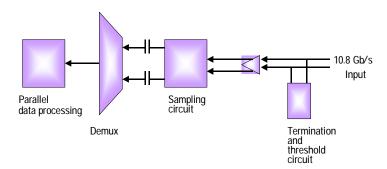

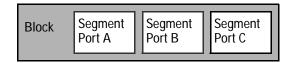

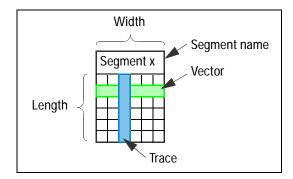

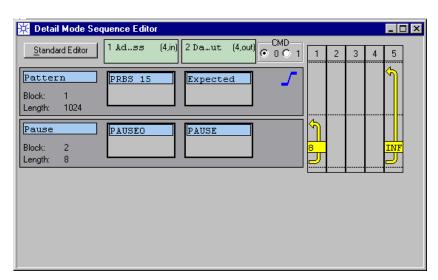

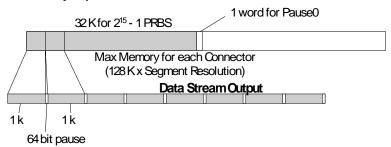

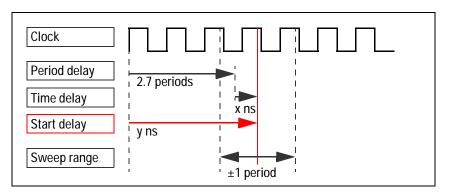

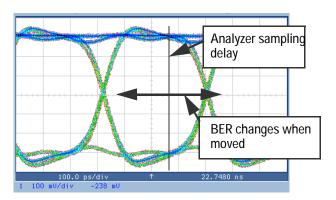

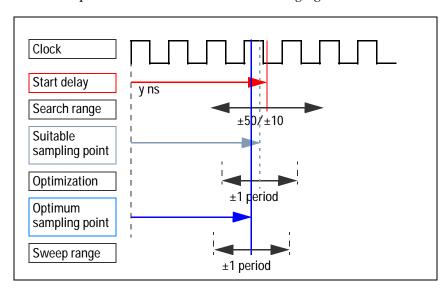

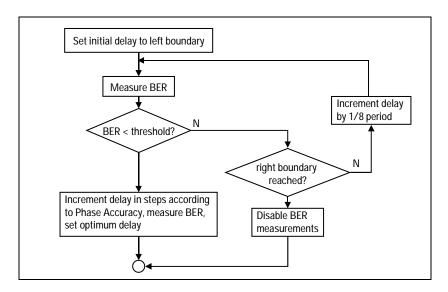

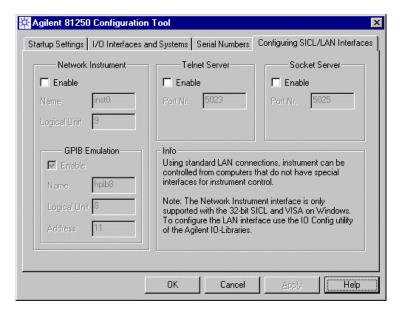

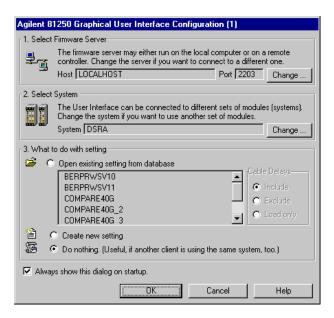

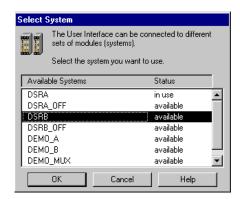

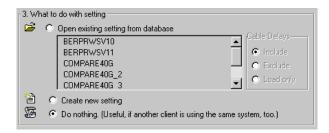

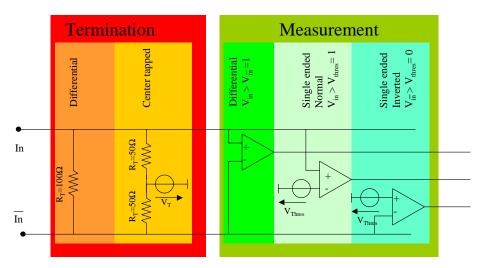

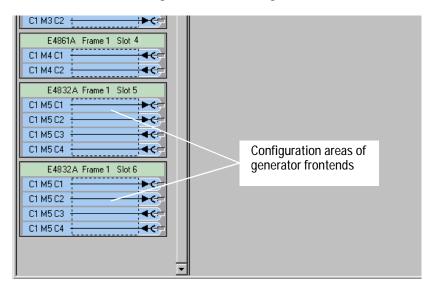

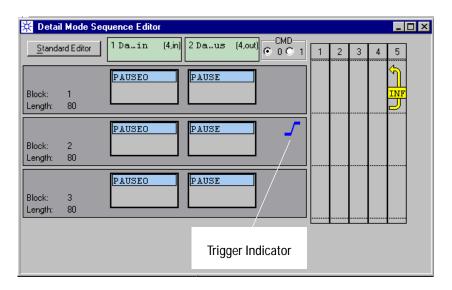

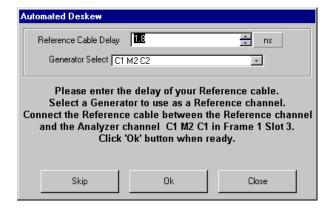

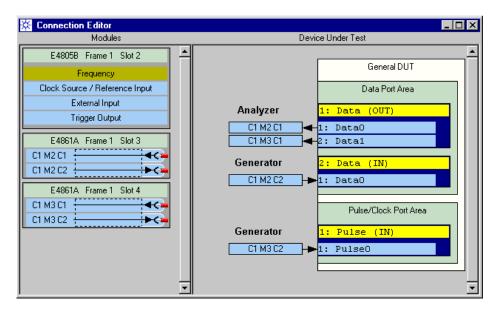

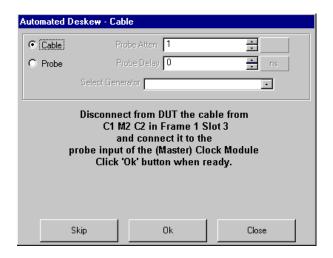

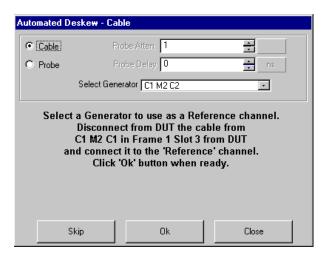

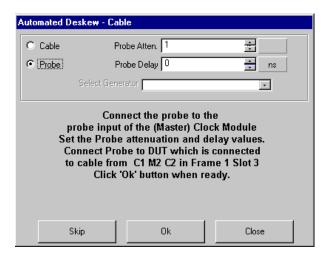

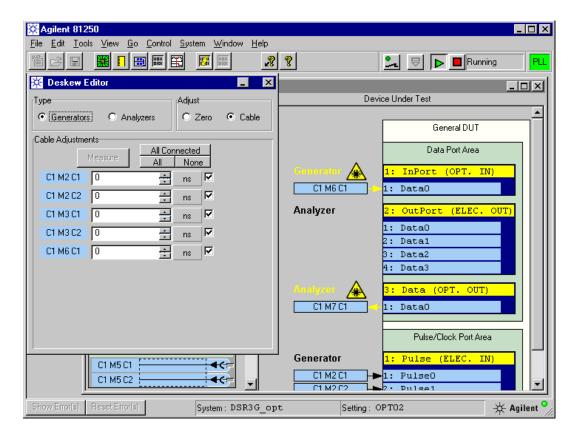

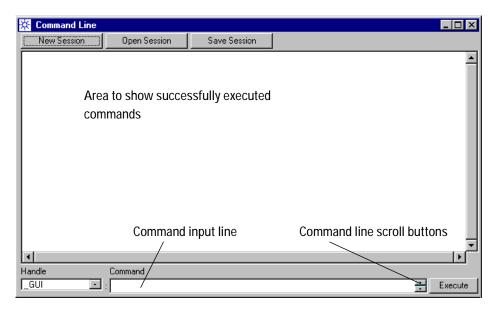

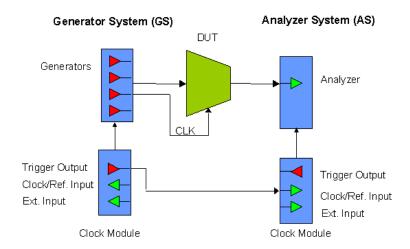

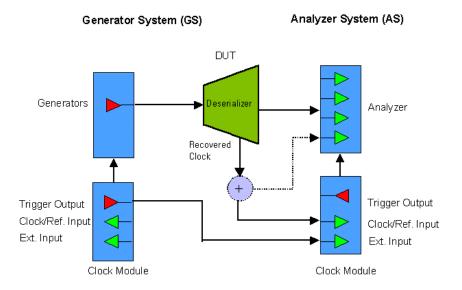

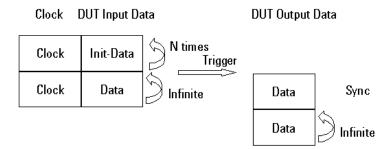

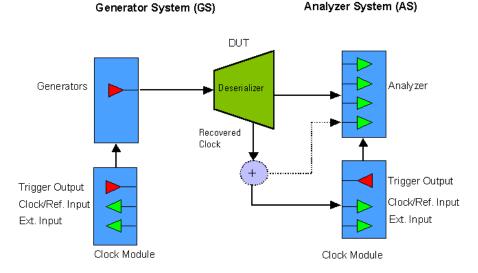

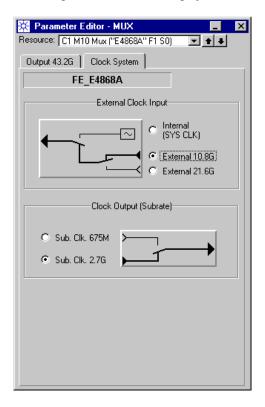

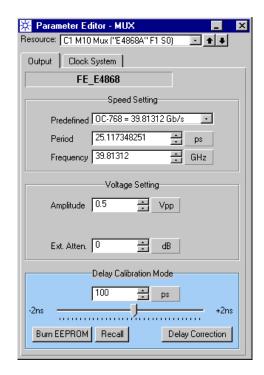

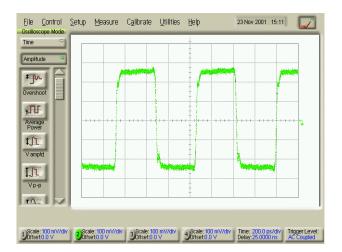

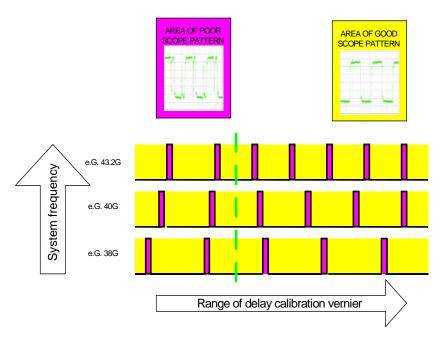

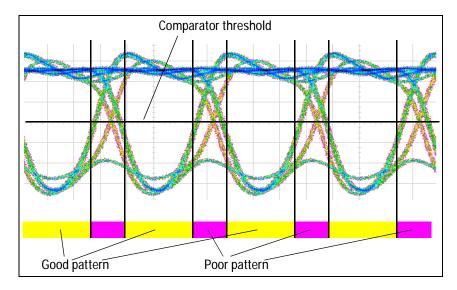

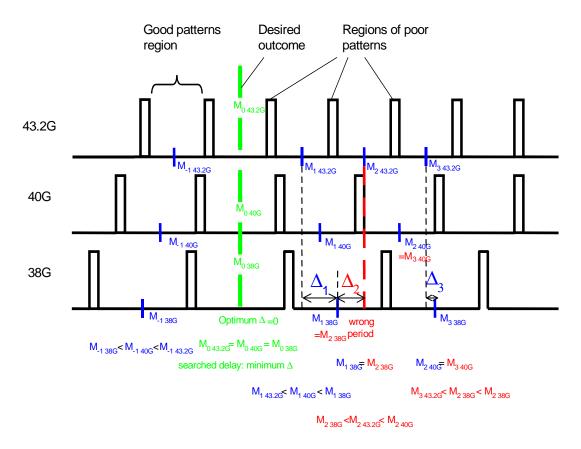

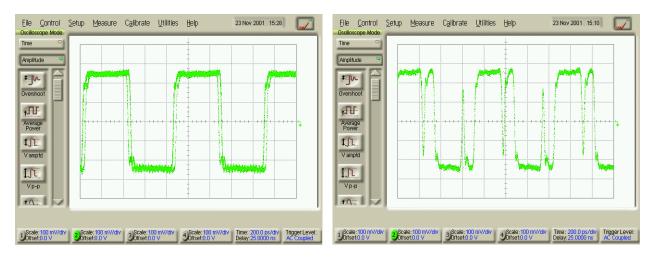

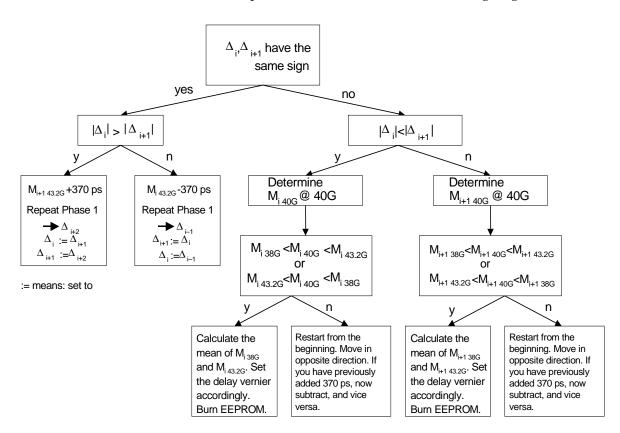

You can switch between optical and electrical operation (see "How to Set the Mode of an Optical-Electrical Connector" on page 209).